Last update $Id$

(c) 2007 BakaOyaji

デザインの検討

図1のブロックダイアグラムを出発点に

、全体のデザインを考えて行きます。PIC16は非常にたくさんの派生製品がありますが、実質的に異なっているのは、命令用のフラッシュメモリの容量、

ファイルレジスタの中のメモリの容量、I/Oなどのスペシャルファンクションレジスタの種類と数です。そこで、CPUをモジュラー化しておけばファイルレ

ジスタを変更すればどのようなPIC16でも比較的簡単に作ることができると考えました。悩ましいのは、いくつかのスペシャルファンクションレジスタで

す。

PIC16では、いわゆる普通のCPUにもある、目的の決まっているレジスタも汎用レジスタ(スペシャルファンクションレジスタ)としてもアクセス

できるようになっているので一工夫必要です。具体的にはプログラムカウンタ(PCLとPCLATH)、ステータスレジスタ、インデックスレジスタ(FSR

レジスタ)です。これらのうちPCLとSTATUSレジスタはCPUに内蔵することにしました。こうしておけば最悪、CPU単体でもなんとか動作させられ

そうです。PCLATHとFSRはレジスタの本体としては、ファンクションレジスタ群に置き必要なときにデータだけ参照するようにします。

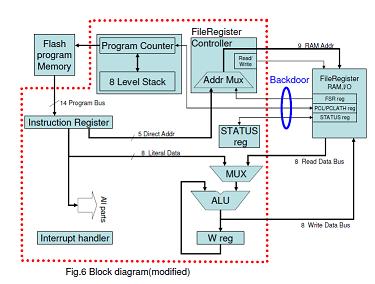

図

としてはこんな感じ(図6)でしょうか?赤の点線で囲った部分がCPUになります。CPUの中は、

図

としてはこんな感じ(図6)でしょうか?赤の点線で囲った部分がCPUになります。CPUの中は、

インストラクションレジスタ

プログラムカウンタ(含、スタック)

ファイルレジスタコントローラ

ステータスレジスタ

インタラプトハンドラ

ステータスレジスタ

マルチプレクサ(リテラルデータ用)

ALU

Wレジスタ

としています。あんまり細かくしても仕方ありません。

青い楕円で示したBackdoorは、スペシャルファンクションレジスタをファイルレジスタ経由でアクセスするパスを確保するためのものです。

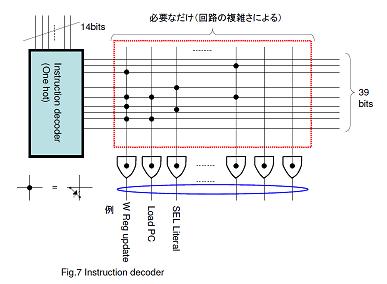

インストラクションのデコーダとしては、なんというか常套手段があります。PIC16の場合、命令数は39種ですから、命令の14ビットから、39出力の

ワンホットのデコーダを作ります。で、これらの信号からCPU内部のF/Fやセレクタの入力へデコーダーをつくるのです。イメージ的には、こんな感じで

す。

各機能は、(一般的に言えば)複数の異なる命令で使われるはずです。したがって、各命令(図7の水平の各線)のORとして表現できるはずです。古典的なマ

イクロプロセッサではデコーダ部分は、図7のようなダイオードアレイのような構造になっているものも少なくありません。この様にしておくと、アレイの部分

を変更するだけで、別の命令セットにできることや、万が一のバグ修正も比較的コストがかからずにできるためでしょう。青の楕円で囲ったところは、個々の

ゲート制御に対応するので、水平化されたマイクロ命令と考えることもできます(ちょっとこじつけっぽいですが)。

なお、CQPICの

実装もおおむねこの方針によるもののようです。

さて、実際のYAP16の実装は上記のような実装ではありません。理由は、

- せっかくなのでVerilogのRTL雰囲気を漂わせたかった(なんじゃ、それ)。

- 全体に小さなモジュールの積み重ねで作りたかった。(なにせ一日のうちとれる時間が限られているので、途中で途切れると次の日に何をやってい

たのかリカバリするのに時間がかかる。笑)

- ちょっと変わったことをしたかった。

で、どうしたかというと、図6のCPUのなかの7つのサブモジュール内で必要な命令デコードもやるようにしました。一種の分散デコーディングですね。

<<前に戻る Index へ 次へ>>