Last update $Id$

(c) 2007 BakaOyaji

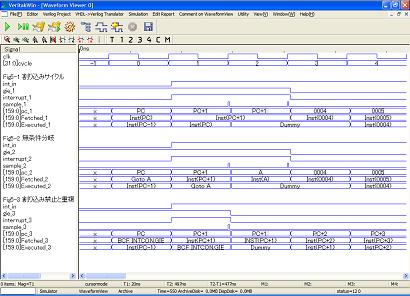

パイプライン実行の検討2

もう少し,パイプライン処理の挙動を考えることにしましょう.今度は割り込みの場合です.例によって,PICmicro

Mid-Range MCU Family Reference Manual(文書番号33023A)を参考にします.11.4 TMR0 InterruptのFigure 11-4: TMR0 Interrupt Timingがだいぶ

判りやすく書かれています.本物のPIC16は4相クロックですが,しぶとく単相クロックで動作させることを考えると,下のFig5みたいになるでしょ

う.

ちなみに,信号名と意味は下表のようになります。

信号名

|

意味

|

| int_in |

割り込み入力 |

| gie_N |

割り込みのイネーブル |

interrupt_N

|

上記2つの信号のAND(CPUへの割り込み信号) |

| sample_N |

interrupt_Xのサンプリングポイント |

| pc_N |

ProgramCounter |

| Fetched_N |

フェッチされた命令 |

| Executed_N |

実行される命令 |

まずは、Fig.5-1 の通常の命令(分岐命令以外)での、割り込み応答サイクルで

す。注目は,CYCLE=2であらわしているサイクルです.このサイクルは割り込み応答サイクルと考えられるでしょう.割り込み応答サイクルで行うべきこ

とは、割り込みのイネーブル信号gieのリセットとISR(割り込みサービスルーチン)へのサブルーチンコールです.サブルーチンコールなので,PCの値

もスタックに退避しておかなければなりません.また,プログラムカウンタは,順調にインクリメントされるわけで,インストラクションレジスタの

「Flush」が必要です.Fig5では,PICのデータブックにあわせ,「Dummy」としていますが,要は,分岐の際の処理と同じ,と考えれて強制NOPを実行するようにすればよいはずで

す.

プログラムカウンタの値は,PC→ PC+1→ PC+1→0004(ISRのベクタ)と変化して生きます.PC+1→

PC+1のところは,割り込みとかがなければ,PC+1→ PC+2と変化するはずですので,PC+1 → PC+1を、GOTO

$と同様に、「分岐」していると考えれば(ちょっとこじつけっぽいですね),分岐したときは,つぎのサイクルは,強制NOPという前のページに書いたのと同じ処理で,CYCLE=2,3のDummyサイクルを実現できそ

うです.

次に、分岐命令と割り込みが同時に起きた場合です。Inst(PC)

が分岐命令の場合が,Fig5-2になります.CYCLE=1で分岐命令が実行されるので,CYCLE=2でのプログラムカウンタの値は,分岐先になり,

割り込み処理ルーチンからの復帰の際はこのアドレスに戻ってこなければなりません.この図では、GOTO命令ですが、CALL命令でもCALLの復帰アド

レスをスタックに積む動作は、CYCLE=1のところで実行されるはずなので問題はなさそうです。

割り込みの発生と,割り込みをマスクをする命令の実行が重なった場合,

気をつけなければならないです.Fig.5-3のように動作すればいいと思います.この場合は,割り込みルーチンへの分岐は起きませんが,1Cycle

のダミーサイクルが挿入されます.たぶん,実際のPICでも同じだと思うのですがちょっと調べようがありません.

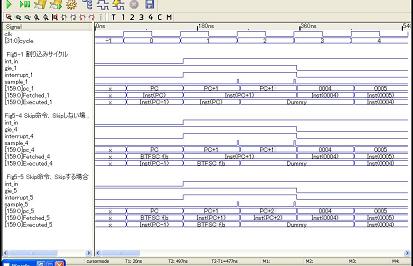

次に,SKIP系の命令の場合を考えます.

SKIP

命令の動作は,命令のフェッチに関しては,通常の命令とまったく変わらず,SKIPする場合は,フェッチした命令を破棄する(強制的にNOPにする)こと

で実現しています.このとき同時にインタラプトが起きると注意が必要

です。

SKIP

命令の動作は,命令のフェッチに関しては,通常の命令とまったく変わらず,SKIPする場合は,フェッチした命令を破棄する(強制的にNOPにする)こと

で実現しています.このとき同時にインタラプトが起きると注意が必要

です。

割り込みが起きた場合は,ISR処理が終了し,元のスレッドに復帰してくるときに,元スレッドでスキップしなかった場合は,(割り込みが起きた時のPC)

+1に,元スレッドでスキップした場合は,(割り込みが起きた時のPC)+2に復帰しなくてはなりません.スキップの条件を,復帰するときまで保存してお

いて、ISRからの復帰時にPC+1に戻るかPC+2に戻るか決める方法もありますが、あまりよいやり方とは思えないので,割り込み処理ルーチンに分岐す

る際に,スタックに積むリターンアドレスをPC+1またはPC+2に変えてやるようにします。

具体的には,Fig5-4,5-5のように動作すればよさそうです.PC+2の「+2」のために特別にハードウェアを用意するのはもったいない(実は+1

と共用できますが)ので,CYCLE=2のとき,プログラムカウンタの値をホールドするのをやめ,普通にインクリメントさせます。ISRにサブルーチン

コールする際にスタックに積むリターンアドレスは、CYCLE=2の時のアドレスですのでこれで望むアドレスになりそうです。

これで,パイプラインの挙動に対する考察はだいたい終わりだと思います.プログラムカウンタ,インストラクションレジスタ,インタラプトコントローラもだ

いたいどんな機能を持たせるかもだいたい決まりました.

なお、このページの波形表示はVeritakを使って、Verilog-HDLのソースコードをシミュレーションしたものです。ソースコードと

Veritakプロジェクトを置いておきます。まあ、本流の使い方ではないですが、Verilogでこんな使い方もあるということで・・・

右クリックで、「ターゲットをセーブ」

<<前に戻る Index へ 次へ>>