Last update $Id$

(c) 2007 BakaOyaji

YAP16 シミュレーションの実行

1. 一般的な注意

ディレクトリ

VerifyとVerigy648の下にいくつかサブディレクトリがあり、それぞれシナリオがあります。Verify以下は、YAP16T84

(PIC16F84A相当)を、Verigy648以下はYAP16T648(PIC16F648A)を対象にしたものです。それ

ぞれのディレクトリには、topXXXX.vというVerilog-

HDLのファイルがあり、これがテストベンチとDUTを含むトップモジュールです。

シミュレータは、Veritak Basic版を

使用しています。Veritakを使う場合は、Veritakのプロジェクトファイル(拡張子 .vtakprj)を開けばシミュレーションできます。

2.シュミレーションを実行する際の注意

Veritakを使う上での注意

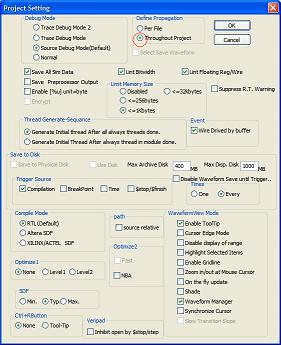

Veritakのプロジェクトのデフォルトでは、`define

の定義はそのファイル内だけで有効ですが、後続するファイルにも定義が波及するほうが一般的だと思うので、そのようにProjectを設定しています(下

図参照)

その他のシミュレータを使う場合

各ディレクトリにある、Veritakのコマンドファイル(veritak_command.txt)を参考にしてください。

3.PICのプログラムのソースコードとHEXファイル

DUT(Device

under

test,

シミュレーションの対象のこと)というインスタンスはPICプロセッサです。これを動作させるにはプログラムが必要です。各ディレクトリには、XXX.asmというアセンブラのソースコードまたはXXXX.cというC言語のソースコードがあります。それぞれ、対応する実行用

のファイルXXX.hexを既に作成してありますが、元のソースコードに変更を加える場合は、次のようにしてください。

アセンブラの場合は、Microchip社のMPLAB

IDE(バージョン、v7.60)のプロジェクトファイルを開いて、アセンブル&リンクを実行して、HEXファイルを作成してください。

C言語の場合は、Hi-tech software社のPIC-C Lite(フリー版)を使用しています。

HEXファイルは、Verilogのテストベンチ内で、Verilog-HDLのシステムタスク

$readmemh()で読める形式に変換しています。なお、Veritakでは独自の拡張として、同様の機能を持つシステムタスクがあります。

2. 各シナリオの簡単な説明

To be written

test0002

このシナリオでは、PORTA/PORTBの読み書きをして、各ポートの動作を確認しています。

サブシナリオとして、top1.asmとtop2.asmがあります。

<< 前へ 次へ >>

Indexへ

トップへ

-------

<>