| Evolve Power Amplifiers | ||||

超低オン抵抗MOS-FETによる整流回路

オン抵抗の極めて低いMOS-FETを整流素子として用いると、大電流を僅かな電圧降下で効率よく整流できるため、低電圧大電流の整流でシリコンダイオードやショットキバリヤーダイオードは時代遅れになりました。

低オン抵抗MOS-FETのオン抵抗は、低いものでは10mΩ以下とリレーの接点並みです。

たとえば10mΩに10A流れても電圧降下は0.1Vに過ぎず、たった1Wの発熱にしかなりません。しかし具体的な回路例は滅多に見ないため自分なりに試行錯誤で実験して作ってみたら、意外と簡単にできたので発表します。

Nch MOS-FETを整流素子として用いる場合は、ドレインがマイナスでソースがプラスの電圧になった時、ゲートにプラスでソースにマイナスの電圧をかけてオンにします。

オーディオアンプの増幅回路ではドレインがプラスでソースがマイナスとなる使い方をすることから、これは意外に思われるかも知れませんが、ユニポーラ素子であるMOS-FETは真空管やバイポーラトランジスタと違って、ドレイン-ソース間の電圧の方向に拘わらず増幅作用をします。

ただし構造上、ドレイン-ソース間にダイオードが存在するために、ダイオードに順方向となる電圧の方向では、ダイオードに電流が流れてしまい、ダイオードの順方向電圧を超える電圧は扱えません。

だから、オーディオアンプなどではダイオードに逆方向となる電圧の方向で使われます。ドレインがマイナスでソースがプラスの電圧の用途を想定したスイッチング用MOS-FETでは、データーシートにドレイン-ソース間の電圧を逆にした場合のソース-ドレイン間電圧(VSD)対ドレイン逆電流(IDR)特性が記載されています。(参考資料 日立: 2SK1297 東芝: 2SK2313 NEC: 2SK2499)

Nch MOS-FETは、ドレイン-ソース間電圧の方向に拘わらず、ゲートにプラスでソースにマイナスの電圧をかけた場合に、ドレイン-ソース間が低抵抗になりオンすることができます。

逆にゲート-ソース間をカットオフ電圧以下にしても、ドレイン-ソース間のダイオードが導通してしまいます。

ドレインがプラスでソースがマイナスとなるダイオードに逆方向の電圧の場合にだけ、ドレイン-ソース間を高抵抗にオフすることができます。MOS-FETがオンしなくてもドレイン-ソース間のダイオードで整流できますが、MOS-FETを低抵抗にオンすることでドレイン-ソース間の電圧ロスが減り、MOS-FETの発熱が少なくなり、DC電圧は増加します。

OPアンプIC一個による超簡単MOS-FET整流器

MOS-FETのドレイン-ソースに加わる電圧の極性を判断して、MOS-FETをON-OFF制御するため、汎用のOPアンプを用いました。

OPアンプの非反転入力にMOS-FETのソースを接続し、OPアンプの反転入力はMOS-FETのドレインを接続して、OPアンプの出力をMOS-FETのゲートに接続してあります。

MOS-FETのドレインがマイナスでソースがプラスの電圧になった時、OPアンプはMOS-FETのゲートにプラスの電圧を与えて、MOS-FETをオンします。

MOS-FET整流器

OPアンプのプラス電源電圧+VCCは、MOS-FETをオンする時のゲート電圧となりますが、ゲート電圧が高いほどオン抵抗が低くなります。

だだし、ゲート電圧の最大規格内でなければなりません。最大ゲート電圧10V程度の品種もあるのでデーターシートなどで規格を確認する必要があります。

大概の品種はロジックレベルに対応していて、ゲート電圧が5Vで充分にオンする特性を持っていますから、OPアンプの+VCCは5V程度とします。

また、OPアンプのマイナス電源電圧-VCCは、OPアンプ内部の差動回路を正常に動作させるために、最低でも2~3Vが必要です。等価的にMOS-FETのソースとドレインが、ダイオードのアノードとカソードに相当し、回路上も置換できます。

Pch MOS-FETの場合

Pch MOS-FETを使用する場合には、OPアンプの接続はNch MOS-FETの場合と同じにしますが、OPアンプのマイナス電源電圧-VCCが、MOS-FETをオンする時のゲート電圧となります。

等価的にはMOS-FETのソースとドレインが、ダイオードのカソードとアノードに相当してNch MOS-FETの場合とは逆になります。

ただ、Pch MOS-FETはNch MOS-FETに比べるとオン抵抗が高く品種も少ないので、ブリッジ整流回路を少ない部品点数で組む場合など位しか用途はありません。

電圧対電流特性

測定回路 横軸はドレイン-ソース間電圧、縦軸は1Ωの電流検出抵抗の電圧で動作電流を表わします。ただし電流検出抵抗の電圧をオシロスコープへ逆極性で入力しているため、縦軸の極性は反転していることを了承ください。縦軸の-1Vは+1Aに換算できます。

また波形にギザギザがあるのは、使用したデジタルオシロスコープの分解能が少ないためで、実際はスムースなラインであることも了承ください。

MOS-FET整流器 2SK1298 (+Vcc=6V,-Vcc=-6V) ドレイン-ソース間電圧のプラス側では、0を境に電流が流れ出し、5Aでのドレイン-ソース間電圧は僅か0.1Vです。オン抵抗は0.1/5=0.02[Ω](20mΩ)であり、5Aの電力損失は5×0.1=0.5[W]と僅かです。

シリコンダイオード 30DF-2

ショットキーバリアダイオード 31DQ6 シリコンダイオードは0.6V位の閾値電圧があり、ショットキーバリアダイオードでも0.3V位の閾値電圧があります。

動作抵抗についてはMOS-FETとチップサイズが違うので対等な比較はできません。

MOS-FET整流器 2SK1298 (+Vcc=0V,-Vcc=-0V) シリコンダイオードの特徴である約0.6Vの閾値電圧があります。小電流では動作抵抗が高いために立ち上がりが緩やかになる所もMOS-FTE整流とは異なるダイオード整流の特徴です。

5Aでのドレイン-ソース間電圧は0.8Vで、5Aの電力損失は5×0.8=4[W]にもなり、放熱対策を要します。

MOS-FET整流器 2SK1298 (+Vcc=3V,-Vcc=-3V) 明らかにオン抵抗が増加していますが、それでもダイオードの比ではありません。数Aの整流ならOPアンプ電源は±3Vでも行けそうです。

MOS-FET 2SK1298 (VGS =5V) ドレイン-ソース間電圧の0を中心に上下左右対称の直線に振れていて、極性の無い20mΩの抵抗体に見えます。

半波整流回路

この回路はドレイン側にAC電源を接続して、マイナス電流を通す半波整流回路です。

半波整流回路 |

|

リップルフィルタコンデンサーは100000μF、負荷として1Ωの抵抗を接続しました。

AC電源電圧をスライダックで可変して0~5A程度まで流してみました。

OPアンプの電源は実験用の安定化電源から得ました。

1Ωに発生する電圧が2V(出力DC電流2A)の時の、MOS-FETの電圧波形を下図に示します。

上の波形はVGS(ゲート-ソース間電圧)で、下の波形はVDS(ドレイン-ソース間電圧)です。

VGSとVDSの波形 (IDC=2A)

VDSがマイナスになる期間では、VGSが+5Vとなりドレイン-ソース間がオンするため、VDSは非常に小さくなっています。

直流出力側にリップルフィルター回路を入れた整流回路では、ゲート電圧の切り替えタイミングがずれると、フィルターコンデンサーに蓄えられた電圧がAC電源側へ逆流して整流効率が低下します。

VDS波形の立上り開始点で生じるスパイクは、VDSがプラスに転じた時点でも、MOS-FETのゲート電極の静電容量に蓄えられた電圧が抜け切らないでVGSがプラスを保っているために、フィルタコンデンサーに蓄えられた電圧がAC電源側へ逆流して発生する現象と考えられます。

スパイク部分は数周期の振動波形をなしています。

フィルタコンデンサーが無ければスパイクは生じないし、フィルタコンデンサーの手前にチョークコイルを入れてもスパイクを防ぐことができます。

しかし、リップルのないDC電圧を得るためにフィルタコンデンサーは必要だし、チョークコイルによる電圧ロスも避けたい。

そこで、OPアンプのプラス入力に-10mV~-20mVのバイアスを与えて、VDSがプラスに転じる前にVGSをマイナスに切り替えるようにしました。

回路図の30kΩと56Ωがそのための回路であり、約-10mVのバイアスを掛けています。

56Ωを100Ωに増やして約-20mVのバイアスとすればスパイクは消滅します。

このバイアスを大きくするとMOS-FETのオン期間が狭くなるので、ドレイン電流のピークが大きくなりVDSが増すために整流効率が落ちます。

全波整流回路

真空管のヒーター直流点火用DC電源としても使える、実用性のあるセンタータップ式の全波整流回路を下図に示します。

全波整流回路

整流するAC電源とOPアンプの電源を共用しているため、3.6Vから12.6Vのセンタータップ付トランスに適用範囲が限られます。

MOS-FETを完全にオンするには4V程度のVGSが必要だから、TL071のプラス電源は最低でも5Vが必要であり、TL071はマイナス電源が最低でも3Vないと正常に動作しません。

OPアンプの電源を別に設ければ、整流するAC電圧の範囲が広がります。2SK1595のオン抵抗は30mΩで、このクラスのMOS-FETは品種が多く価格も安い(@200円台、若松通商)ので使用してみました。もちろんよりオン抵抗の低い品種を用いた方が性能が向上することは云うまでもありません。

2SK1595では出力電流が2A程度までなら発熱は少ないが、3A以上では放熱板が必要になります。

オン抵抗の低い2SK1298なら3Aでも発熱は少ないです。

2SK1298を使用する場合は、56Ωを100Ωに変更しないとスパイクノイズが出ます。

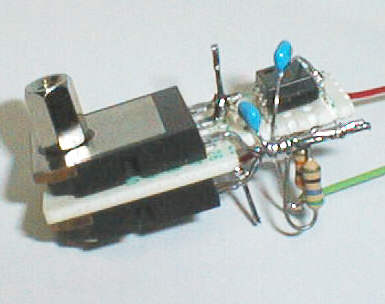

全波整流ユニットの製作

全波整流ユニットの回路 |

|

| 入出力特性 | ||

|

条件 | OPアンプ電源:±6V 負荷抵抗:1Ω リップルフィルターコンデンサー:10000μF |

|

||

高電圧整流仕様

これまでの回路は低電圧(6V以下)の整流を前提にしていたために、OPアンプ

ICの耐電圧を考慮していませんでした。

MOS-FETのドレイン-ソース間にはAC電源電圧(実行値)の2.8倍の電圧が発生しますが、それがOPアンプの反転入力側の許容する電圧を超えてはならない制約がありました。

そこで、そうした不具合を解消して、高いAC電源電圧まで使用できるように改良しました。

高電圧整流仕様 |

|

※印のダイオードとMOS-FETの耐電圧は、AC電源電圧(実行値)の2.8倍以上が必要です。

図の実験回路で VAC=100V の時、1kΩ負荷に発生した電圧は113Vでした。

無負荷ではAC電源電圧が0Vの時でも、OPアンプ回路の電圧が1S1832を通して出力に発生します。

そのため、AC電源をOFFするだけでなく、OPアンプ電源もOFFしないと、DC

OUTを完全に0Vにできないことを考慮しておく必要があります。

Copyright © 1998 Shinichi Kamijo. All rights reserved.

最終更新日2006/09/07 23:33:22 +0900