V A L V O R G

6336 CSPPパワーアンプの

設計から製作まで

|

|

Semiconductor reinforced vacuum tube amplifier V A L V O R G

|

| 32Ωマッチングトランス装着仕様 6336 CSPPパワーアンプの 設計から製作まで |

|

|

|

VALVORG (バルボーグ)とは半導体アンプの一部に真空管を取り入れた回路を意味するものとして私の考えた

valvetic organism の短縮形造語です。

真空管と半導体の混在回路の総称として従来用いられるハイブリッドという名称は、真空管回路が順次部分的に半導体と置換わって行く時代のものと捕らえ、半導体回路が進化した現在においては逆に半導体アンプの一部を真空管に置換えることで真空管の風味をアンプに与えるという発想を元にした回路をバルボーグと名付けてみました。

またもう一つには、真空管だけでは実現しなかった理想的な回路構成を半導体で補うことで具現化して、いわばアンプとして最強のものを目指そうという趣旨の Semiconductor reinforced vacuum tube circuit 半導体強化真空管回路という概念も含んでいます。

以前にカメさんから頂戴した32Ωのマッチングトランスを活用して、電気料金を気にしないで長時間使用できるように、消費電力をせめて電気コタツの弱並の150W程度に収めつつ、 真空管OTLの味を持つ実用的なアンプを製作しようと思います。

使用する出力管は1本の管に独立した2つのユニットを持つ6336を選びました。

この2ユニットをクロスシャントプッシュプルで使用して、チャンネル当り1球のステレオアンプとします。

設計に当って先ずはじめること、データ収集。

データシートはインターネットで検索すると簡単に入手できます。

6336のデータ

データシートから最大規格や動作特性が概ね判ります。

しかしデータシートには、これから製作するアンプのように低い負荷インピーダンスで動作させるために必要な大電流域の特性図がないので、現物を入手して実測でデータを得るしかありません。

入手した6336は写真の CETRON JAN 6336B 同一製造ロット(93A 72241 8635)の4本です。

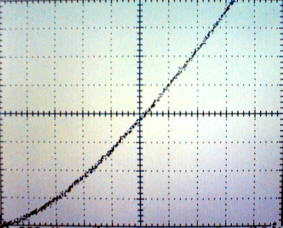

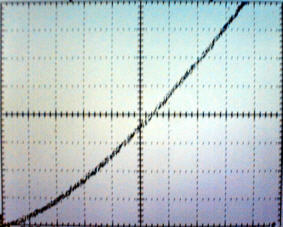

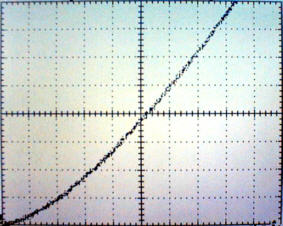

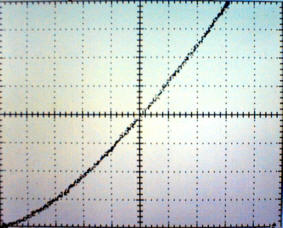

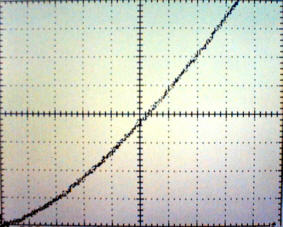

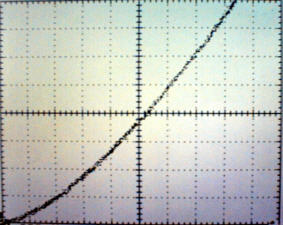

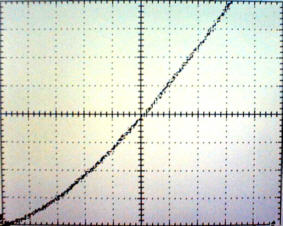

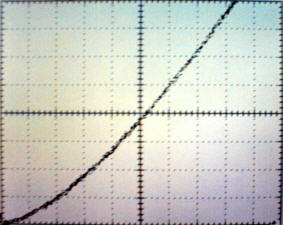

4本の球にNo..1〜4の番号を付けて、図1の回路でEc=0Vの時のEp-Ip特性をオシロスコープで測定しました。

〔図1〕 Ep-Ip特性測定回路

測定した時のオシロスコープの写真を以下に示します。

横軸がEpで1目盛りが20V、左端が0で右端が200V、

縦軸がIpで1目盛りが200mA、下端が0で上端が1600mAです。

| ユニット 1 | ユニット 2 | |

| No..1 |  |

|

| No..2 |  |

|

| No..3 |  |

|

| No..4 |  |

|

4本の特性に大きなバラツキは無く、ユニット間も大体合っています。

特性は揃っているのに、惜しいことに印刷の位置が1本だけ反対面になっています。

6336の片ユニットのプレート電流の最大規格は400mAですが、これは平均値であるため、連続正弦波の最大値は400mAにπを掛けた1256mAです。

単発波形ならもっと大きな電流でも時間平均が400mAであれば許されると思いますが、時間に関するデータが無いので分かりません。

プレート損失の時間平均が最大規格をオーバーしなければよいとしても、大きな電流を得るためには高いプレート電圧を掛けなければならず、そうすると信号出力時にはプレート損失の最大規格をオーバーする度合いが

増えますから、大出力は瞬間的にしか許されず常時は小出力で球を労わるように使う必要があります。

また、プレート損失

を減らすためにアイドリング電流は少なめな設定とせざるを得ず、アイドリング電流の少ない程、絶対的変化幅が変わらなくても相対的変化量が大きくなるので、アイドリング電流の変動を抑える必要があります。

前述の如く連続正弦波の最大値に縛られることはありませんが、取りあえず Ipmax=1256mA、RL=32Ωと定めて、最大出力を Po=Ipmax2RL/2 の計算式で求めると約25Wと相応の出力が得られるので、下図のようにロードラインを引いて動作点を求めました。

〔図2〕 6336Bの動作点

Ipmax=1256mAとEc=0のカーブとの交点のEpminは142V、電圧振幅は1256mA×32Ω=40VなのでEpmax=142V+40V=182Vとなります。

電源のレギュレーションを考慮してプレート電源電圧を190Vとします。

下表に示すEp=190Vの時のEc対Ipの実測データから、無信号時にIp=50mAとするなら、Ec=-65Vとなります。

| Ec (V) | -55 | -60 | -65 | -70 |

| Ip (mA) | 120 | 80 | 50 | 30 |

回路を実験する

動作点の検討結果を基に、下図のような回路を考えました。

〔図3〕 アンプ回路

〔図4〕 電源回路

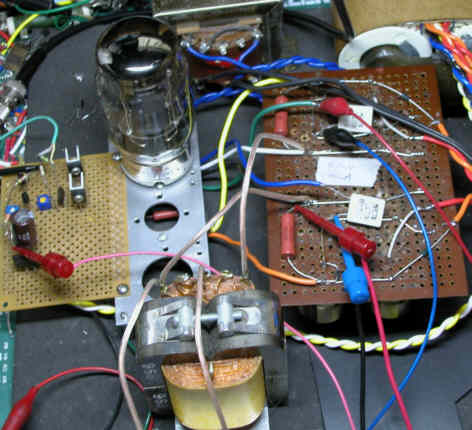

実験には電圧を可変できる電源を使ったり、要所を可変抵抗器で調整できるようにして、電流、電圧、波形等の観測を行います。

実験中の様子

電源トランスは例によってフェニックスで造って頂きました。

電源トランスの1次側にスライダックを入れて電圧を可変出来るようにしています。

ヒータ電源は別で常時点灯状態です。

最大出力がクリップ直前で20W得られます。これは連続波出力のために電源電圧が180V以下までの低下があっての値ですから、電源電圧の低下を招かない瞬時のバースト波なら計算通り25Wは得られると思います。

しかし、如何せんオープンループゲインが少ないため、出力インピーダンスは5Ωと高く、負荷に直流抵抗の少ないマッチングトランスを接続したことで、僅かなDCドリフトでもアンバランス電流が生じてマッチングトランスに大きなDC電流が流れるために実用性に乏しい状態です。

対策としては、出力をコンデンサでDCカットするとか、初段負荷を定電流源にしたり増幅段数を増やすとかでオープンループゲインを上げるとか、DCサーボを掛けるとか、等など従来ある手法を使えば解決可能でしょうけど、どれももっさりしていて今一触手が伸びません。

もっとスッキリ簡単に出来ないものかと思っていたら、自分で以前に考え出した方式が使えるではないかと気付きました。

ムゲンダイン回路を追加して実験

ムゲンダイン回路とは、NFBアンプの非反転入力と反転入力の間に発生する電圧(NFBアンプのエラー電圧)をキャンセルする電圧を入力電圧に加算することで、見かけ上エラー電圧0の動作をする理想NFBアンプに変えてしまうと云うものです。

基本的には野呂さんのD-NFBアンプから発想したもので、ZDRとかと同じです。

〔図5〕 ムゲンダイン回路付アンプ回路

マッチングトランスの32Ω端子からNFBを掛けているので、出力インピーダンスを32Ω端子で測定して0ΩとなるようにVR1を調整します。

8Ω端子の出力インピーダンスを0Ωにすると、32Ω端子では負性インピーダンスになり、最悪ラッチアップして出力が正負どちらか一方に張り付いてしまう危険があるので、VR1の調整は慎重する必要があります。

VR1はアイドリング電流調整で6336Bの無信号時のプレート電流を50mAにする。

VR2はPSDCのゲイン調整で、電源のDC電圧変動に対して6336Bの無信号時のプレート電流が一定となるようにする。

VR4はDCバランス調整でマッチングトランス32Ω端子のDC電圧を0Vにする。

V1〜V5の電源は同じ電源トランスから得ている非安定化電源なので、DC電圧の変動率は同じですが、短時間の変動に対しては同じではないので、PSDCはリップル電圧などには効果がなく、電源電圧のDC的な変動に対してアイドリング電流を一定に保つだけの作用です。

+15V と-15Vは実験用安定化電源から供給しています。

1W出力時の歪率は、100Hz 0.004%、1kHz 0.006%、10kHz 0.04%

周波数特性は、100kHz -0.5dB、150kHz -0.9dB

出力インピーダンスは、8Ω端子で0.2Ωですが、これはマッチングトランスの巻線抵抗に他なりません。

無入力時のノイズが0.5mVと大きく、それが電源リップルではなくてホワイトノイズです。

入力信号源の内部抵抗が変わるとオフセット電圧が変わります。これは2SJ109のVgsのペアバランスが悪いために起きる現象と思います。

方形波出力にリンギングが生じ、帰還抵抗に並列のコンデンサでリンギングの様子が変わり、出力振幅を上げるとリンギングは大きくなります。

実用化にはまだ改良の余地が多分にありますが、特性的には申し分ありません。

しかし特性に6336の存在感が無くなり寂しいような想いになるのは、登りつめた者の宿命にある贅沢と云うものでしょうか。

やはりこれまでの6336の性格という腐れ縁を保ちつつ行くべきか悩む所です。

6336の存在感を惜しむより、この回路のユニークさを尊ぶべき、と意を決して実用に向けて改良を加えて行くことにします。

ムゲンダイン回路を変更

図5の回路でも入力にバッファーが必要であることが分かったため、バッファーを使うことが前提ならということで、図6のような反転型ムゲンダイン回路で実験してみました。

〔図6〕 反転型ムゲンダイン回路付アンプ回路

パワーアンプ回路の初段は入力と直結しないので、FETを取り去りトランジスタだけにしましたが、ミラー効果で歪率が悪化しています。

方形波出力のリンギングは全く無くてすっきりしています。

周波数特性も、100kHz -0.3dBと良好です。

しかし別な欠点があり、VR1の調整で出力インピーダンスを小さくすると出力にDCが発生し、VR4の調整範囲を超えて6336Bのプレート電流がアンバランスとなります。

そしてそんな状況下で悲劇が発生しました。

6336Bをお釈迦にする

慣れとは恐ろしいもので、始めの内はおっかなびっくりでやっていたものの、まるで6336Bの存在を感じさせない特性に、ついつい調子こいてへまをやってしまいました。

皮肉にもこんな結末で6336Bの存在感を痛切に思い知らされるとはと、我が身の愚かさを呪います。

プレート電流のアンバランスによってマッチングトランスにDC電流が流れてインダクタンスが減少している状態でありながら、出力を増加させたために

過大なカソード電流の発生し、6336Bの両ユニットともカソードと電極を接続するリボン状のヒューズが溶断して、球を1本お釈迦にしてしまいました

リボン状のヒューズはカソードの溶接部分から途中の折曲げてある所までが熔け落ちて球状の金属が散っています。庭の雪もまだ融け切らないというのに、何とと云うことだろうか、でもこれで6336Bの限界は見極めたことだし、これからの私は今までの私とは違うとはずだから、気を取り直し、実験再開。

DC全帰還化

直流抵抗の小さいマッチングトランスを直結するからには、出力にDCが発生しないようにすることを第一に考えるべきであったと反省しました。

そこで図6を眺めると、入力バッファーの反転入力側が御誂え向きにDC全帰還が掛けられることに気付き、図7のように改良しました。

〔図7〕 DC全帰還化反転型ムゲンダイン回路付アンプ回路

DC全帰還の効果は素晴らしく、出力には1mVもDC電圧は発生しません。ハイゲインなオペアンプに無限大ゲインの回路を従えたDC全帰還のループゲインは天文学的数値であろうと想像するしかありません。

6336Bとマッチングトランスにマッチングした回路の誕生です。

このアンプのテーマを『マッチング』と云うことにしようと思います。

シミュレーションによる検討

容量負荷による発振の防止策をシミュレーションで検討してみました。

6336のSpiceモデルは以下のような内容にでっち上げました。

Ep−Ip特性は図8のようになり、実際のデータと大体フィットしています。

| * at the following conditions: * plate voltage : 0..400v * grid voltage : 0..-140v * cathode current: 0..50ma * * * connections: plate * | grid * | | cathode * | | | .subckt 6336 p g k *e1 2 0 value={v(p,k)+2.725*v(g,k)} *r1 2 0 1.0k *gp p k value=697e-6*(pwr(v(2),1.5)+pwrs(v(2),1.5))/2} bp p k i=697e-6*uramp(v(p,k)+2.725*v(g,k))^1.5 cgk g k 13.7p cgp g p 15.2p cpk p k 4.7p .ends 6336 |

〔図8〕 6336SpiceモデルのEp-Ip特性

〔図9〕シミュレーションした回路

6336のアイドリング電流が約50mAとなるようにI1を6.64mAに設定しました。

R10は実際の回路では歪最小となるように設定しますが、ここでは正帰還量を大目に設定して、より安定性の悪い条件を仮定しています。

偶然の発見でしたが、C2(5pF程度)を接続すると容量負荷に対して安定になりました。

C2は高域ゲインを低下させる作用があります。

負荷にC1の0.1μFを接続した場合の方形波応答を図10に示します。

〔図10〕 0.1μF負荷時の過渡解析

ムゲンダイン回路の危険性

ムゲンダイン回路は負帰還が掛からなくなると正帰還の歯止めが無くなってラッチアップ状態になり、出力に電源電圧を放出しつづける可能性のある非常に危険な代物です。

負帰還が掛からなくなる状態は、出力段がカットオフか飽和の状態になると発生します。

ただしカットオフの状態では出力が無くなるため支障ありません。

どんな回路でも危険性がありそれを認識して回避する対策が取られているから実用化できているわけで、ムゲンダイン回路も確実な対策ができれば安心して実用に出来るものと確信します。

実用化策を施したムゲンダイン回路

出力段が飽和状態で不安定になるのを防ぐために、正帰還量を減らしてムゲンダインの効果を無くすスイッチ回路を設けて、6336のグリッド-カソード間電圧が0Vに近付いた時にそのスイッチを入れるようにしました。

図11の2SJ103がそのスイッチです。

ついでにそのスイッチを手動で操作してムゲンダイン無しの6336本来の音色を楽しむ余興を追加しようと思います。

PSDC回路をこれまでの簡略的な電源の直流電圧変動に対してだけ働くものから、より完全な個々の電源を直接に監視して制御するものに変更しました。

これにより6336のバイアス電圧はその時点のプレート電源電圧とグリッド電源電圧を元に計算された値に設定されるため、電源投入のシーケンスなど考えなくてもよく、リップル分などでプレート電流が変化するのも抑えられるので電源を簡略化できます。

〔図11〕 ほぼ固まりつつあるアンプ回路

〔図12〕 ほぼ固まりつつある電源回路

〔図11〕 ほぼ固まりつつある電流制限回路

出力管の保護を目的に出力管の電流を制限をする回路を備えました。

最悪でも出力管の内部抵抗とマッチングトランスの巻線抵抗で電源電圧が分圧されるため、スピーカにダメージを与えるほどのDC出力電圧は発生しませんが、その代わりにマッチングトランス

に過大なDC電流が流れて出力管がお釈迦になる可能性が高いので、出力管のカソード側に定電流回路を入れて電流の上限を制限する方法を採りました。

このMOS-FETによる定電流回路は大きな帰還容量と高いゲート側インピーダンスの作用でACでは定電流性が無くなるため、ピーク電流を0.47Ωに発生する電圧で検出

し、DC電流を定電流回路の電圧の増大で検出することが出来ます。

ピーク電流は1,5A程度、DC電流は0.3A程度で作動するように設定して、過電流が1箇所に発生すると全部の定電流回路をカットオフします。