ここで展開する実験によって、従来設計の増幅段は絶対に必要か、それがもたらす性能が本質的に重要だったのかを見直そうと思います。

アンプ構成のリストラには根本的な改革が必要ですが、ああだこうだと机上の空論を述べているより、実践主義の私としては、ここは一番より少ない段数で十分な性能が得られるアンプを作ってみるしかない訳で、たとえできなくても何が課題かを見つけられるだけでもいいし、そこから派生するテーマで新たな道が開けるかも知れないと考えます。

| Evolve power amplifiers |

2ステージ構成の限界に挑戦する 2SJ200/2SK1529 パワーアンプ

| [1]最初の実験回路 | 大概のパワーアンプは、初段、ドライブ段、出力段、さらに出力段の手前にソースフォロワが入るなどで3段以上のステージで構成されていますが、この段数が少ないほど音の劣化は減ると予測できます。 ここで展開する実験によって、従来設計の増幅段は絶対に必要か、それがもたらす性能が本質的に重要だったのかを見直そうと思います。 アンプ構成のリストラには根本的な改革が必要ですが、ああだこうだと机上の空論を述べているより、実践主義の私としては、ここは一番より少ない段数で十分な性能が得られるアンプを作ってみるしかない訳で、たとえできなくても何が課題かを見つけられるだけでもいいし、そこから派生するテーマで新たな道が開けるかも知れないと考えます。

|

|---|---|

| [2]改良回路 | |

| [3]Crss対称化回路 | |

| [4]エミッタフォロワドライブ追加 | |

| [5]初段FET並列接続 | |

| [6]出力段ソースフォロワ/オーバーオールNFB | |

| [7]出力段ソースフォロワ/オーバーオール帰還無し | |

| [8]初段回路 | |

| [9]カプリオ・クアッド回路 | |

| [10]MOS-FETの逆特性を利用したPP回路 | |

| [11]交叉型出力回路の実験 | |

| [12]改良版電圧増幅回路 | |

| [13]2SJ200/2SK1529パワーアンプ 第1号 | |

| [14]2SJ200/2SK1529パワーアンプ 1号改 | |

| [15]2SJ200/2SK1529について | |

| [16]2SJ200/2SK1529 ボルテージミラー | |

| [17]2SK2313金田式 | |

| [18]逆立ち型 | |

| [19] 初段改逆立ち型 | |

| [20] 減帰還ソースフォロワ逆立ち型 | |

| [21] ZDレベルシフト方式 NFBタイプ | |

| [22] ZDレベルシフト方式 無帰還タイプ | |

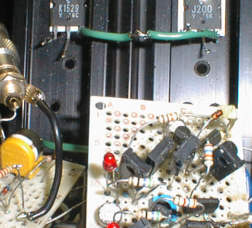

[1] 最初の実験回路 これは実験の取っ掛りに最初に試した回路です。 これは実験の取っ掛りに最初に試した回路です。初段はコンプリメンタリー差動回路で、出力段はソース接地動作のコンプリメンタリープッシュプル回路とし、パワーアンプとして最小限の2ステージ構成としました。 100Ωの可変抵抗器で2SJ200/2SK1529のアイドリング電流を0.5A程度に調整します。 このアンプのオープンループゲインは負荷インピーダンスが低いほど減少するため、負荷インピーダンスに反比例して出力抵抗が増加し、8Ω負荷で出力抵抗が0.8Ωならば、4Ω負荷では出力抵抗は1.6Ω、逆に16Ω負荷では出力抵抗は0.4Ωという具合に負荷インピーダンスが高いほどダンピングがよくなり、負荷インピーダンスが低くなると急激にダンピングが悪くなります。 出力段のMOS-FETはドレイン電流の少ない部分でVGS-ID特性曲線の湾曲度が大きいため、アイドリング電流が0.1A程度では大きな第3次高調波歪みを発生します。 MOS-FETは電圧入力素子でドライブ電流は必要ないのですが、周波数が高くなるとCissの充放電に電流が消費されるため初段差動アンプの電流振幅が大きくなり第3次高調波歪みが増加します。 |

[2] 改良回路 この回路は最初の2ステージ構成は守りながら、大幅に改良を加えた回路です。 2個ある1kΩの可変抵抗器で出力DC電圧をゼロに保ちながら2SJ200と2SK1529のアイドリング電流を0.5A程度に調整します。

初段差動回路は大きな電流振幅に耐えるようにゼロバイアス動作として、初段FETの電流が増加したためカスコード接続によってドレイン損失の増加を押さえました。 最初の回路では差動回路の片方の出力しか用いてませんでしたが、この回路では差動出力を有効に使うためカレントミラープッシュプル回路に変更しました。 方形波にツノ(オーバーシュート)が出ていたため、帰還抵抗10kΩと並列に10pFを入れて取りました。 |

||||

[3] Crss対称化回路 この実験では2SJ200と2SK1529のCrssのアンバランスを解消するため、対称となる側と同じMOS-FETをゲート-ドレイン間に接続しました。イメージでは下図のような感じです。追加したMOS-FETはバリキャップ(可変容量ダイオード)として作用します。

8Ω負荷で1Wの時の歪み率が100Hzの場合0.0015%、1kHzの場合0.003%、10kHzの場合0.02%となり、歪みの成分はどの周波数も第3次高調波が主体で、第2次高調波の発生を無くすことに成功しました。

コンプリメンタリープッシュプル回路のCrssのアンバランスで発生する第2次高調波はこの手法で解消できそうです。これを『コンプリメンタリー・バラスト方式』とでもしておきます。 |

|||||

[4] エミッタフォロワドライブ追加 出力段MOS-FETの前にエミッタフォロワ回路によるドライブ段を追加した回路です。 初段の負荷容量が小さくなったため、高域におけるオープンループゲインの低下が減り、高域歪みが大幅に減少しました。

エミッタフォロワ段を加えたため、2段構成で行く当初の目標から逸れて3段構成になりました。 |

||||

[5] 初段FET並列接続 増幅段数を増やさずに、オープンループゲインを上げる手段として並列接続があります。 この実験では初段FETを並列接続してgmを2倍にし、特性の改善を試みてみました。

やはり高い周波数ではオープンループゲインの低下によって歪み率が悪化します。 2SJ109/2SK389はシングルインラインパッケージで左右対称にピンが配列されているため、基板の裏側からピン同士を向かい合わせに半田付けして並列接続することができます。この技を名付けて『表裏対向並列接続』。

|

|||||

[6] 出力段ソースフォロワ/オーバーオールNFB これまでは出力段がソース接地動作でしたが、今回から出力段をコンプリメンタリーソースフォロワとしました。 初段の負荷インピーダンスが高いため、オープンループゲインが高くなり、オーバーオールでNFBをかけた場合は歪み率が非常に低くなりました。

これまでの回路では出力段のアイドリング電流が多いほど歪み率が低下しましたが、この回路では0.3A程度で歪み率が最小になります。 図6の出力インピーダンスは1kHzで0.02Ω程度と非常に低くなりました。 22pFは方形波のリンギングを取るために付けましたが、無くても発振しません。 |

||||

[7]出力段ソースフォロワ/オーバーオール帰還無し 前回の回路を、初段のみのマイナーループNFBに変更して、出力からのNFBを廃しました。 初段の出力インピーダンスがNFBによって低くなっているため、出力段MOS-FETのCrssのをドライブする能力が高くて、周波数による歪み率の差が無くなったと思ったのですが、初段だけの歪み率は非常に低く、また初段の負荷インピーダンスを低くすると歪み率が増大する事から、出力段が発生する大きな歪みで初段の歪みがマスクされていると判断できます。

歪み成分は第2次高調波が主体です。1kHzの第2次高調波は0.04%で、第3次高調波は0.003%でした。 この回路ではアイドリング電流が多いほど歪み率が低下します。 出力インピーダンスは1kHzで0.3Ωと、以前のソース接地動作場合と同程度になりました。

|

||||

[8] 初段回路 初段の回路を研究するため、初段部分だけで実験しました。 VR1でDCオフセット電圧の調整をできるようにしてあり、VR2で第2次高調波歪を最小に調整できるようにしてあります。 この回路を説明すると、まずQ1,Q2,Q3,Q4のJ-FETで構成されるゼロバイアス・コンプリメンタリー差動回路が増幅作用を行いますので、これが、この回路全体の中核部分です。

この回路の歪み率は非常に低いですが、やはり周波数が高くなるに連れ、負荷が重くなるに連れて歪み率が増加します。 |

||||||||

[9] カプリオ・クアッド回路 これは初段差動回路の直線性を改善するため、Q1,Q2,Q3,Q4のMOS-FETで構成されるカプリオ・クアッドという回路を用いた実験です。 Q1,Q2はソースフォロワとしてQ3,Q4をドライブしているので、増幅はQ3,Q4が行います。Q3,Q4のソースは定電流源と電流帰還抵抗(VR1)に接続してあります。 実験してみると、Q1,Q2,Q3,Q4に使用したMOS-FET 2SK1398のノイズが大きいため期待したほどの成果は得られませんでした。表はVR1=100Ωのデータです。

VR1の抵抗値を小さくするとゲインが上がります。ゲインを上げてNFBを強力にした方が歪みは小さくなります。VR2は動作電流を調整するためで、動作電流が大きいほどMOS-FETのgmが上がり歪みが減ります。VR3で2次歪を最小に調整してあります。 VR1を小さくし過ぎたり、過大入力を与えると突然発振状態(周波数は高くない)になります。発振する原因は恐らく、Q3,Q4のゲートとドレインがたすき掛けに接続されている様は正にフリップフロップ回路であり、Q3,Q4の一方が飽和状態になるとリニアな制御ができなくなって、マルチバイブレーターに変身してしまうのではないかと考えられます。 この回路で次にやる事は、Q1,Q2の動作条件をQ3,Q4の動作条件に限りなく近づけけるため、①Q1,Q2のドレインソース間電圧をQ3,Q4と等しくなるように、カスコード接続する。②Q1,Q2のゲート側のインピーダンスがQ3,Q4と等しくなるようにソースフォロワでドライブする。他に②Q5,Q6の定電流回路をカスコード化する。③Q1,Q2,Q3,Q4に使用するMOS-FETのペア選別を厳格にする。④Q1,Q2,Q3,Q4にローノイズ特性のものを使用する。⑤Q1,Q2,Q3,Q4に入力容量の小さいものを使用する。⑥定数の検討等です。 |

|||||||||

[10] MOS-FETの逆特性を利用したPP回路 MOS-FETのVDS-ID特性は左図のように、VDSを通常と逆に与えた場合でも、VGSでIDを制御できます。 この制御は、MOS-FETドレイン-ソース間の寄生ダイオードの順方向電圧(約0.6V)を越えない狭い範囲で有効です。 その逆特性は、飽和することのない3極管特性であり、VGSのカットオフ電圧は低くいので、正特性と逆特性に対称性はありません。 |

左図の回路は、上述の非対称性を承知の上で、正特性で動作するQ5と、逆特性で動作するQ6をプッシュプルで使用した実験回路です。 ドライブ回路が簡単に差動アンプでできることが、この方式の唯一の利点です。 Q5,Q6のバイアスはVR2で調整しますが、Q5よりもQ6のバイアスを低く設定する必要があるため、Q1の定電流回路でQ6のVGSを引き下げて、VR1によってDCバランスの調整をできるようにしました。 Q7,Q8によるカスコード回路で、Q5,Q6のVDSを0.6V以下に保ようにしました。 Q9,Q10とQ11,Q12はQ7とQ8にバイアス電圧を与える回路で、VR3,VR4でQ5,Q6のVDSを0.5V程度に設定しました。 このアンプの出力段はソース接地動作で、フローテング電源の中点から出力を取り出す方式です。 このアンプの特性は、出力波形を見て分るほど、プラス側が肥大する2次歪みを生じました。 正特性で動作するQ5のVDSは1V以上ないと直線性が悪くなりますが、逆特性で動作するQ6のVDSは0.5V以下でも良好な直線性が得られるので、何か面白い使い方ができそうです。 |

カスコード接続動作のVDS-ID特性 正特性側(Q5,Q7側)特性-赤線 逆特性側(Q6,Q87側)特性-青線 |

[11] 交叉型出力回路の実験 あらゆる可能性を確かめたくて、かつて真空管OTLに使われていた、交叉型出力回路を実験してみました。 あらゆる可能性を確かめたくて、かつて真空管OTLに使われていた、交叉型出力回路を実験してみました。交叉型出力回路は、出力段にフローティング電源を必要としますが、完全対称動作をするため、2次歪みの発生が少ないことが期待できます。 この回路は無帰還で、2SK1529による出力段はソースフォロワです。 フローティング電源のためか、ノイズが大きいことが欠点です。

実験中に過電流が発生して2SK1529が2本とも壊れてしまい、その後は怖くてこの回路の実験を行ってません。 |

[12] 改良版電圧増幅回路 これまで様々な回路を実験しましたが、[8]で実験した回路に勝る方式が現時点では見つからないので、それをベースに改良を加えて特性の改善を図りました。 これまで様々な回路を実験しましたが、[8]で実験した回路に勝る方式が現時点では見つからないので、それをベースに改良を加えて特性の改善を図りました。主な改良点は、安定化電源を加えてノイズを減らしたことと、カレントミラー回路をコンプリメンタリー式にして、最終カスコード段トランジスターのベース側インピーダンスを下げて、ミラー効果による影響を減らしたことですが、100Hzと1kHzの歪率は電源ノイズの減少で改善されましたが、10kHzの歪率は期待に適わず改善されませんでした。

|

[13] 2SJ200/2SK1529パワーアンプ 1号 [12]の回路にドライブ段と出力段を追加して、実用可能なパワーアンプとしてまとめた回路です。 VR1によって電圧増幅段の電源電圧を40Vに設定します。VR2で無信号時の出力DC電圧を0Vに設定します。

上の表は、2SJ200/2SK1529のアイドリング電流が0.5Aに置けるデーターです。 その後ノイズレベルを下げる手段として、NFB回路のインピーダンスを下げると効果的であることが確認できました。 ノイズが減ると歪みが見えてきて、そしてもっと歪みを減らしたくなります。 |

[14] 2SJ200/2SK1529パワーアンプ 1号改 ドライバーのエミッタフォロワで発生する歪みを抑えるため、出力段のバイアス回路の帰還ループに、ドライバー・トランジスターのベース-エミッタ間を入れる回路に変更しました。 これによって、アイドリング電流が前回より少ない0.4Aでありながら、10kHzの歪み率は0.001%を余裕で下回ることができました。

|

| [15] 2SJ200/2SK1529について 2SJ200/2SK1529はオーディオ用に開発されたパワーMOS-FETで、バイポーラトランジスターやUHC MOS-FETと呼ばれる低ON抵抗パワーMOS-FETに比べると、飽和電圧が高く電源利用効率の点で不利ですが、ドレイン・ソース間の耐電圧が高いので、大パワーを望なら電源電圧を高くす事で可能です。最大電流は単発パルスで20Aまで許容してますから、並列接続しなくても±35Vの電源電圧では、音楽信号なら2Ωの低負荷インピーダンスまで余裕をもって対応できます。 電極間静電容量が大きい代わりに大電流が流せてgmが高いことが特徴のUHC

MOS-FETは、オーディオアンプにはおよそ無縁の大電流領域でないとカタログ通りの高いgmが発揮されません。 |

[16] 2SJ200/2SK1529 ボルテージミラー 容量負荷に対して安定だが、高域周波数特性は悪いが、出力段をエミッタフォロワでドライブすれば改善される可能性がある。 容量負荷に対して安定だが、高域周波数特性は悪いが、出力段をエミッタフォロワでドライブすれば改善される可能性がある。出力オフセット電圧を小さくし、第2高調波歪を減らすには、初段FET 2SJ103/2SK246のペア選別が不可欠。 ボルテージミラーFET 2SJ44/2SK163の代わりに2SJ103/2SK246を使用した場合は出力インピーダンスが高い。 |

[17] 2SK2313 金田式SEPP出力段 金田式対称アンプのドライブ段をコンプリメンタリー・フォールデット・カスコード・プッシュプルとした回路。 金田式対称アンプのドライブ段をコンプリメンタリー・フォールデット・カスコード・プッシュプルとした回路。アイドリング電流は温度上昇と共に減少する。 オープンループゲインが低いため、容量負荷安定性は高いが、出力抵抗が高くダンピングファクターが低い。 アイドリング電流を増やすと出力段MOS-FETのgmが上がるため歪み率が下がる。 高域周波数特性は悪いが、出力段をエミッタフォロワでドライブすれば改善される可能性がある。 |

[18] 逆立ち型 この回路の出力段は実験[10]でも使ってますが、ラジオ技術に藤井秀夫氏が発表した逆立ち型と呼ばれる方式です。 この回路の出力段は実験[10]でも使ってますが、ラジオ技術に藤井秀夫氏が発表した逆立ち型と呼ばれる方式です。

出力段MOS-FETのソースを接地しているため、電圧増幅段の出力電圧は出力段MOS-FETのVGSをスイングするだけの小さな振幅でよいので、電圧増幅段の電源電圧を低く出来ます。 出力段の電源が接地から浮いていて、出力段の電源と接地間の浮遊容量がスピーカーと並列に入ることになります。 初段2K246/2S103のどちらかgmの大きい側にソース抵抗を入れて2次歪みを最小に調整してます。 出力方形波に派手なリンギングを生じたため、帰還抵抗1kΩに200pFを並列接続して方形波の角を丸めました。 初段2K246/2S103はgmとVGSのそろったコンプリメンタリーペアーですが、温度特性と電極間容量には大きな違いがあり、そのため歪みやドリフトが発生します。 |

[19] 初段改逆立ち型 初段をデュアルFETに交換したことで歪と温度ドリフトが大きく改善されました。 初段をデュアルFETに交換したことで歪と温度ドリフトが大きく改善されました。

2SK389と2SJ109のソースを回路図のようにクロスさせても結合しても特性に何ら変化ありません。 |

[20]

減帰還ソースフォロワ逆立ち型 この回路は出力段がソースフォロワの帰還率を減らした動作をする方式です。出力段MOS-FETのソースが接地から浮いているためノイズが大きく、その点ではこの方式は失敗でした。 この回路は出力段がソースフォロワの帰還率を減らした動作をする方式です。出力段MOS-FETのソースが接地から浮いているためノイズが大きく、その点ではこの方式は失敗でした。

出力段の電源と接地間の浮遊容量が帰還抵抗1kΩと並列に入るため、高域特性も悪く100kHzの方形波が3角波になります。その浮遊容量をキャンセルするため、0.1μFと68Ωの直列回路を47Ωと並列に入れ、100kHz方形波が再現できるように高域特性を調整しました。反面容量負荷には強く発振しません。

|

[21] ZDレベルシフト方式

NFBタイプ [14]の回路のフォールデットカスコードの部分をツェナーダイオードに変更して部品点数を減らした。 [14]の回路のフォールデットカスコードの部分をツェナーダイオードに変更して部品点数を減らした。そのため電圧増幅段の電源電圧が2倍必要になる。 ツェナーダイオードが通電しないとNFBが作用しないため、電源オンオフ時に1V以上のショックノイズを発生する。 歪率などの特性は[14]と変わらないから、ショックノイズの問題がなければ合格なのだが残念ながら失格。

|

[22] ZDレベルシフト方式

無帰還タイプ [21]の回路のオーバーオールのNFBを廃して無帰還化し、ショックノイズを減らした。 [21]の回路のオーバーオールのNFBを廃して無帰還化し、ショックノイズを減らした。

電圧ゲインは2SK389/2SJ109のソース抵抗220Ωと2SC2856/2SA1191のエミッタ抵抗4.7kΩの比で決まる。 出力段はソースフォロワで出力インピーダンスは0.3Ω程度になるから実用可能。 歪み率は、1kHz 1W RL=8Ωの時0.03%程度。

|

2段構成アンプは、初段(入力段)と終段(出力段)で構成されるが、各段のゲイン配分に相違があっても、オーバーオールでNFBを掛けると特性に大差ないことが分った。

出力段がソースフォロワの場合、初段が全ての電圧ゲインを稼ぐことになり、出力段入力の電圧振幅が大きい。出力インピーダンスはソースフォロワの作用で低くなる。その上、初段の余剰ゲインが出力インピーダンスを下げる。

一方、出力段がソース接地の場合、初段は出力段MOS-FETのゲート・ソース間電圧をドライブするだけの電圧で良いから出力段入力の電圧振幅は小さい。出力インピーダンスは出力段のゲインと初段の余剰ゲインで低くなる。

ゲイン配分が違ってもトータルのゲインが等しければ出力インピーダンスは等しいから、出力段がソースフォロワと出力段がソース接地では、使う素子が同じであれば出力インピーダンスは等しいことになる。

どちらの方が素子にとって楽な動作であるかで性能に差が出来ると考えられ、初段の電圧振幅の小さい出力段がソース接地の方がよさそうだ。

しかし出力段がソースフォロワでは、ソースフォロワがマイナーループで出力段のゲインを出力インピーダンスの低減に換えているからオーバーオールの帰還量は少ないが、出力段がソース接地では出力段のゲインも初段に回しているため、オーバーオールの帰還量が大きく、その副作用が心配だ。

アイドリング電流の少ないB級プッシュプル動作出力段は、完全に特性の等しい素子を用いた対称回路と云えども、本質的に3次歪みを発生する。

小出力時はスピーカーの駆動力が弱く、出力が増すほどに駆動力が高まるから、歪み波形は頭を尖らせるパターンだ。

これを音楽に躍動感を与えるエキスパンド効果と好意的に受け止めることができれば幸せだが、小出力時は本来のパワーが出ない異状動作をしているのではないかと真相を突かれてしまうと立つ手がない。

駆動力を高め3次歪みを減らすには、アイドリング電流を増やすか、出力段にNFBを掛けることが有効だ。

Nチャンネル素子とPチャンネル素子で構成されるコンプリメンタリープッシュプル出力段は、特性が完全に対称な素子は存在しないので2次歪みを発生する。しかし実際はアイドリング電流の少ないことによる3次歪みが大きく、それに比べたら2次歪みは少ない。

Copyright © 1998

Shinichi Kamijo. All rights reserved.

最終更新日:2000/11/05 21:12:13 +0900