2SJ18 CSPP OTLパワーアンプの製作

30W+30Wステレオ

|

2SJ18 |

2SJ18はSIT(V-FET)だ。

回路はシンプルな非対称ドライブ2段構成とした。

電源のV1、V2は接地してあるので、他のチャンネルと共用できる。V3、V4は出力電圧の上に乗っかっているフローティング電源だ。

初段は差動アンプで、入力信号の与える側でドライブする出力段はソースが接地してあるから、ドライブ信号電圧の振幅は、出力信号電圧の1/μである。

初段差動アンプの反入力側でドライブする出力段のソースは出力端子に接続してあるため、ドライブ信号電圧の振幅は、出力信号電圧の1/μに出力信号電圧を加えた値と大きい。

しかし差動アンプの反入力側はゲート接地動作であるため高域特性は優れている。

2SJ18の入力容量はパワーFETとしては比較的少なく、その上μが小さいために、ミラー容量が小さい。

この回路では2SJ18のゲートに多量の電流を流してまでドライブすることは出来ないため、負荷がショートしてもドレイン電流はON抵抗で制限されて過大な電流とはならない。

2SJ18はgmが低いので温度補償のないラフなバイアス回路でもアイドリング電流の変動が小さい。

2SJ18はVgsが一定だとVdsに比例してIdが変化するため、Vdsに比例してVgsを変化させることでIdの変化を減らすようにした。

やってみなければ分からないというか、案ずるより産むが易しで、接地電源とフローティング電源のトランスのコアが共通でも特性に影響ないようだ。

V1、

V4電源は電流が少ないので倍電圧整流で得た。同様にV5も倍電圧整流にしてみたが、ノイズが0.3mV以上あり、V5を別電源としたことでノイズが0.1mV以下にできた。

V1、 V4のリップルが同位相でないとノイズが桁違いに大きくなるので配線に注意を要する。

初段には耐圧の高いFETが必要だ。V-FETの2SK79ではゲインが低くてNFBを掛ける余裕がないが、3極管無帰還アンプ並みのダンピングファクタにはなるから、それはそれで面白い。耐圧80VのJ-FET 2SK223ではダンピングファクタ8程度になる。入力容量が気になったが試しにMOS-FETの2SK215を使ってみたらダンピングファクタが16になり、高域特性は変らなかったのでこれに決定した。

入力のCRは、入力の信号源インピーダンスを高くすると出力方形波にオーバーシュートが発生したため、それを殺すために設けた。

初段差動アンプの定電流回路のトランジスタ(2SC1815)のエミッタ抵抗(2kΩトリマー抵抗)で、電源電圧の変動に対する2SJ18のアイドリング電流の変化を調整できる。2kΩトリマー抵抗の抵抗が小さいと、電源電圧の上昇でアイドリング電流は減少し、トリマー抵抗の抵抗が大きいと逆に電源電圧の上昇でアイドリング電流は増加するので、電源電圧が変化してもアイドリング電流が変化しないように調整する。

2SK30Aはによる定電流回路の電流を10kΩトリマー抵抗で可変して2SJ18のアイドリング電流を調整する。

2kΩトリマー抵抗でも2SJ18のアイドリング電流は変わるが、ほぼ1kΩ付近に最適位置があるので、2kΩトリマー抵抗はセンターを中心に僅かに動かすだけにして、10kΩトリマー抵抗でアイドリング電流を調整するのがコツだ。

この回路のアイドリング電流を一定にする作用は電源電圧の速い変化には追従できないので、電源リップル電圧には2SJ18のドレイン電流は変化する。しかしプッシュプルバランスが取れていれば電源リップルの影響は出力には現れない。

プッシュプルバランスは初段差動回路のソース抵抗(50Ωトリマー抵抗)で、出力のDC電圧を0にすることで調整出来る。

最大出力は8Ω負荷で25W程度、出力電圧波形の最大が20Vで頭打ちになるから、2SJ18には10V程喰われている。

2SJ18のアイドリング電流は0.3A程度とした。

Zo 0.5Ω

100kHz -0.5dB

THD 0.01%

2SJ18は、Id=-1A、Vds=-5Vの時と、Id=-0.2A、Vds=-30Vの時のVgsを測定してμを算出し、μが近いものをペアとした。

今回使用した2SJ18は数年前に若松通商が販売していたもので、昔、2SK60とコンプリで購入したものよりもIdssが大きい。

実験ではストックの2SK215を使用したが、新規購入に当って値段の安い2SK213を採用した。2SK213は2SK215よりも耐圧が低いだけで他の特性は変わらない。これもId=2mA、Vds=40Vの時のVgsを測定して、Vgsの近いものをペアとした。

電源トランスはいつもRコアトランスを特注しているが、今回は汎用品が使えるので、RSコンポーネンツが取り扱っているトロイダルトランスを使用してみた。1次側が115V仕様のため100Vで使用すると 2次側の電圧は0.87掛になる。

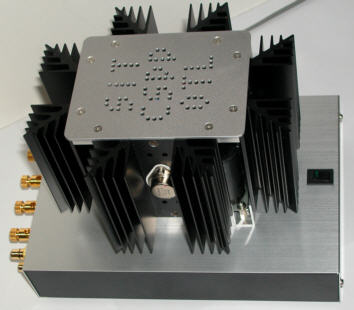

放熱器(ヒートシンク)もRSコンポーネンツから取り寄せた。TO3Pの取付け穴の加工済品だ。放熱器の形がアンプのデザインを決定する。

電解コンデンサや整流ダイオードなどは若松通商の特価品を中心に集めた。

若松通商やRSコンポーネンツはインターネットで注文できるから便利だ。

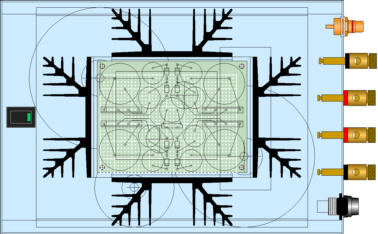

シャーシレイアウト

ケースはタカチYM-250(250×170×50)。内部にトロイダルトランスを3個収納。放熱器の囲いの中に電源基板とアンプ基板を取付ける。

トロイダルトランスを側面の際に付けてしまうと下ケースを被せられなくなる。

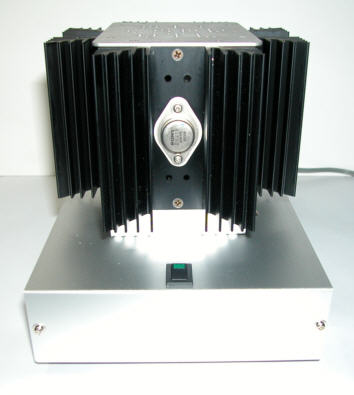

フロントビューのデザインイメージ

放熱器を高床式に取り付けることで下から空気が流れるようにした。

パワースイッチ内蔵のLEDにより正面の2SJ18が照らされる効果を期待する。

正面の2SJ18をドレインがアース電位の方にするので、御本尊がむき出しでも問題ない。

製作した回路。

破線枠内の回路はチャンネルごとに必要。Q1とQ2を熱結合する。Q3とQ4は各々1.4℃/Wヒートシンクに取付。指定なき抵抗は1/4W。コンデンサの耐圧は50V以上

実験回路からの変更点はアイドリング電流の検出抵抗を2SJ18のドレインに入れたことと、電源電圧が使用する電源トランスの仕様に伴って変ったことくらい。

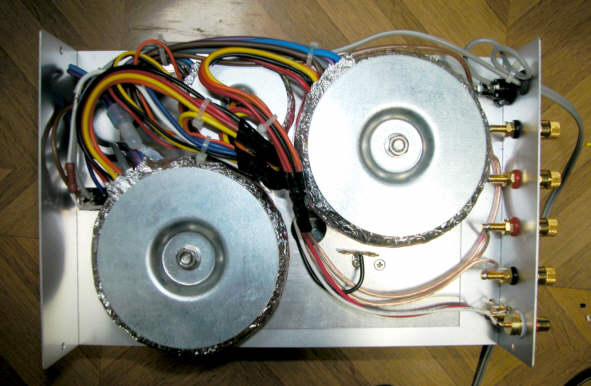

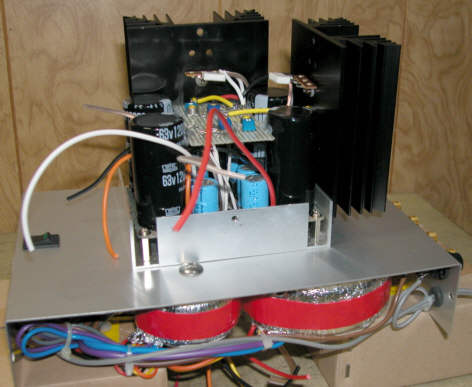

出来上がった基板をテスト中。

左側のトロイダルトランスの上にあるのが電源基板で右側の放熱器の上にあるのがアンプ基板。

アンプ基板のトリマー抵抗は基板の配線面側に配置した。

このテストのの段階で調整は出来ている。

アンプ基板を電源基板の所定の位置に据える。

電源基板のブロックコンデンサの谷間に、2SK213を下に向けてアンプ基板 を取付ける。このような配置は現物の寸法に合わせた造りになるので、実際に使う部品が決まり、それを手に

して見てからでなければに考えられない。

この後、アンプ基板の支柱(スペーサ)が2SJ18の取付ネジに干渉して邪魔であるため、アンプ基板をブロックコンデンサにホットボンドで固定して、支柱を取り去った。 この組立構造の変更を招いた要因は寸法の読みに誤算があったというか、そこまで綿密に考えていなかったためだ。

トランスで埋め尽されたケース内部。

ケースに強度を持たすため2mm厚アルミ板を敷いた。

トロイダルトランスをアルミホイルで包み静電シールドした。トロイダルトランスのリード線の引出し口は漏れ磁束が多いので、そこを向かい合わせにしないように取付ける。

複数のトロイダルトランスの取付方法を検討するに当って色々実験してみた結果、ドーナツを重ね合わせする配置では結合があることが判ったので横並べに決定した。接触させると結合が増えるので少しでも離すようにした。静電シールドは効果的で、できれば引出し線もシールドしたいくらいである。アルミホイルがドーナツの穴の中でつながるとアルミホイルに誘導電流が生じショート状態となるのでしてはいけない。また取付ボルトに上下両方でアルミホイルが触れることがないように注意が必要である。

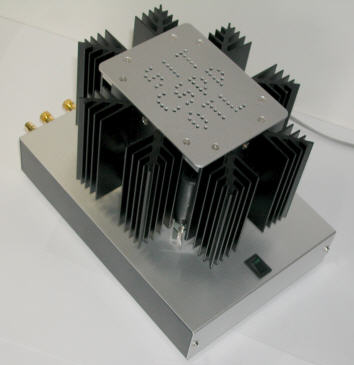

基板の四方に2SJ18を取付けた放熱器を取付けて行く。

毎度のことのような気がするが、自分の作るアンプは配線が非常にやり難い。ミスしてやり直しなんてことは考えたくもない、もう勘弁してよといいたくなる2度は作りたくないと思う作業だ。

CSPPは同じ様な配線が2組、ステレオアンプだから4組存在するため、それを取違えないよう、細心の注意を要する。配線コードと接続ポイントに施したペイントマーカーによる色分けで管理することによって間違えずに配線できた。

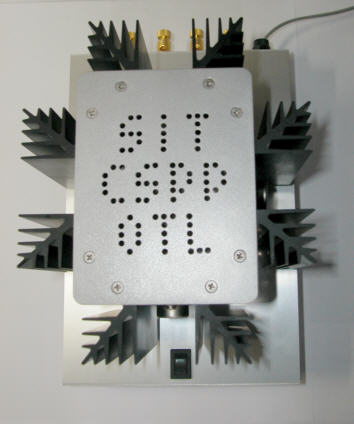

B5の雑誌サイズで一見軽そうだが、実は電源トランスが3個も入っているのだからヒョイとは持ち上がらない。

対称に配置された放熱器の幾何学的な形にイメージするものは黒い雪の結晶だろうか。大骨の連なりがクロス状に見える造形はCSPPアンプにこそ相応しいと評価できる。

特性図は全てLチャンネルのデータである。

入力電圧対出力電力特性 RL=8Ω ,f=1kHz

オシロスコープの波形で確認したクリッピング開始出力は33Wだった。

周波数特性 RL=8Ω ,0dB=1V,f=1kHz

20kHzまではフラットで30kHzで-0.05dB、100kHzで-0.45dB、300kHzで-2.8dBだ。

歪率特性 RL=8Ω ,残留ノイズ0.2mV

テスト組立での残留ノイズは0.1mV程度だったが配線処理の問題だろうか、Rチャンネルは0.1mVを下回っているが、Lチャンネルは大きい。

ノイズが減れば100Hzの小出力におけるTHDはもう少し減る。

1W以上の出力の歪の主成分は3次歪だ。2SJ18のアイドリング電流を増やせば改善されるが、このデータに不満はない。

出力インピーダンス特性 ON-OFF法による,RL=8Ω /∞ Vo=0.8V

5kHzまで0.43Ω(8Ω負荷に対するダンピングファクターは18.6)、10kHzで0.44Ωになり、周波数が上がるとと共に増加し100kHzで0.72Ωとなる。

チャンネルセパレーション特性 信号源出力電圧1V(RL=8Ω )

漏れ信号を検出するアンプ側の入力をショート状態で測定した。

両チャンネル共に5kHzまでは残留ノイズ以下で変化ない。

最大出力時(出力電圧16V)でも両チャンネル共に5kHzまでは残留ノイズ以下で変化なく、その場合のチャンネルセパレーションは-100dB近くとなる。まあこれは電源が独立しているのだからそうなるのが当然だ。

Lチャンネルは残留ノイズが大きいだけでなく、Rチャンネル側の信号を拾い易い。

原因はRチャンネルの出力信号の乗っている部分が、Lチャンネルの入力側に接近していて信号の飛びつきが起きているのか、Rチャンネルの出力信号の流れる配線がLチャンネルの配線と共通になっていると考えられる。

両チャンネルを同じに配線したつもりだが、全く対称の状態ではないので、その辺に何か原因があるのだろう。

基板のテスト時にこのようなことも確認しておけばよかったのだろうが後の祭りだ。分解して再度組み直す気力はもうない。

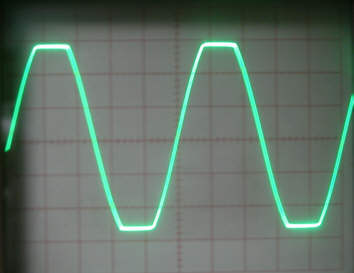

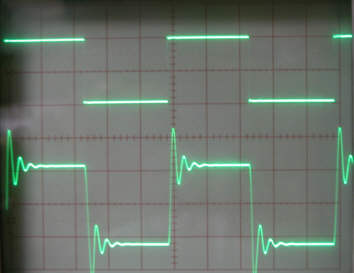

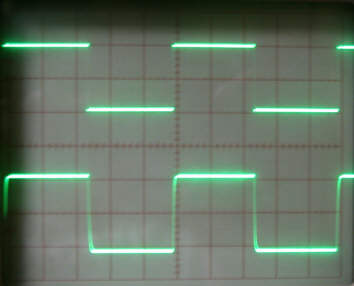

クリップ波形

出力40W(1kHz)

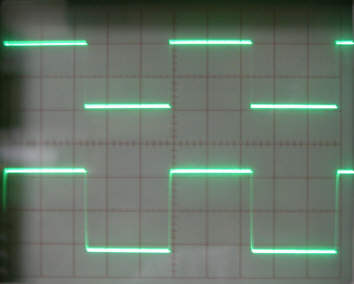

10kHz方形波波形

上:入力

下:出力 0.5V/div

無負荷

0.47μF負荷

8Ω負荷

0.47μFと8Ω並列負荷

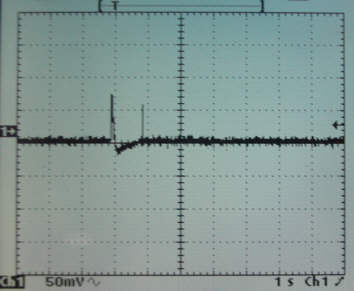

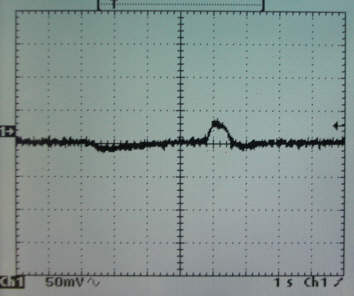

ショックノイズ波形 50mV/div

電源投入時

電源遮断時

|

最終更新日 2005年01月01日 |