一日一回路 vol.2

2002/7/12

クロス結合フィードフォワードAB級出力段

IIN1とIIN2は入力電流で、これが0である無信号時における出力トランジスタのQ3とQ4のICは、

D1のVFとQ2のVBEが等しく、D2のVFとQ3のVBEが等しい場合に、D2とQ3がカレントミラー回路を形成しているので、Q3のコレクタ電流はIR4に等しくなり、同様な関係でQ4のコレクタ電流はIR3に等しくなる。

つまり、Q3とQ4のアイドリング電流はIR3とIR4によって決まる。

D2がQ3の、またD4がQ4の温度補償になっているから、互いの熱結合を密にして温度条件を揃えることが肝心だ。

従って温度安定性は既存の熱結合に頼る方式と変わらないだろう。

IR1とIR2はQ1とQ2のVBEをD1とD2のVFに等しくするためのバイアス電流と考えられる。

D1のVFとQ2のVBEが等しい場合にD1のIFとQ2のICが等しいならば、また、D3のVFとQ1のVBEが等しい場合にD3のIFとQ1のICが等しいならば、IR1=IR2=IR3+IR4であり、IR3=IR4ならば、IR1=IR2=2IR3=2IR4である。

2002/7/13

出力段にMOS-FETを使う場合は下図のように、Q3とQ4のそれぞれのVGSに等しいMOS-FETを、ゲートとドレインを接続してD3とD4の代わりにするとよいだろう。

大入力時はQ1とQ2の内のどちらかがカットオフするので、オープンゲインがステップ状に増加することが考えられ、変な歪が出そうな気がするから、IR1とIR2の所へ並列にダンプ抵抗を入れた方がよいかも知れない。

下図は適当に考えたアンプ回路の1例。

2002/7/15

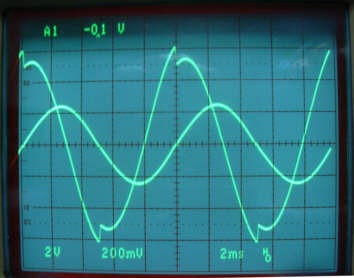

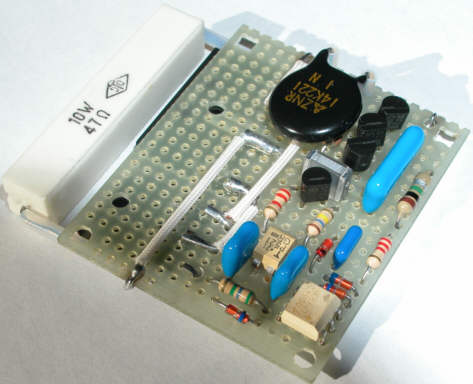

クロス結合フィードフォワードAB級出力段の実験

実験はデュアルトランジスタを使って必要な熱結合を得た。

いたずらに回路が複雑化するのを避けるため電流源は抵抗に置き換えた。

4.7kΩは

カットアンドトライで求めた歪率最小となる抵抗値で、これより大きくても小さくても歪が増す。

出力にDCオフセット電圧が+0.2Vほどを生じる。これは使用したトランジスタのHFEがNchとPchで違うことが原因と思う。

歪率は1kHz、2.8Vrms出力に置いて、無負荷で0.018%、100Ω負荷で0.7%である。

歪成分の波形を見た感じから、クロス結合トランジスタがカットオフすることが原因で発生する歪と思われる。

出力段の最小コレクタ電流は4.7kΩの電流に等しくなるため、カットオフすることのないA級動作だが、代わりに、クロス結合トランジスタがカットオフして非直線歪を発生するとは皮肉な回路だ。

歪を無くすにはクロス結合トランジスタがカットオフしないように充分なバイアス電流を与えてA級動作とするしかないだろう。

出力インピーダンスは1kHzで1.6Ω。

1kHzで3Vrms出力時の入力電圧は150mV、この時の反転入力と非反転入力間の信号電圧は1.8mVだったから、NFB量は38dB程度。

150Ωの部分を電流源にするならば、もう少しオープンループゲインが上がり、歪率と出力インピーダンスが下がるかも知れない。

周波数特性は2MHzまで観測したが、レスポンスはまったく低下する気配が無く、流石に電流帰還型アンプは凄い。

2002/7/27

ムゲンダインアンプ

NFB AMP

上図に示すNFBアンプは、

Vo=Vi/β である。

Aのゲインが無限でない限りVeが存在し、

Vi=Vs-Ve となるから、

Vo=(Vs-Ve)/β となる。

Ve にはAの歪が含まれているため、

Aの歪がなくならない限り、

歪のない増幅はできない。

Mugendyne AMP

NFBアンプのVeを上図に示すようにVsに加算すると、

Vi=Vs+Ve-Ve となり、

Veが消去されて、

Vi=Vs となるから、

Vo=Vs/β となるため、

歪のない増幅が可能になる。

見かけ上、INとNFB間に電圧が発生せず、

開ループゲインが無限大になることから、

ムゲンダイン(Mugendyne)アンプと命名した。

200/2/8/14

バイフェーズ方式の回路は以下のようで、

アースは電源の極性の基準点を示すために設けましたが、そこがアースされている必要はありません。

タイミングは以下のようです。

2002/8/15

直結オール真空管SEPPアンプ

超3結バージョン1の帰還管は、出力管のプレートとグリッドの電圧ギャップを橋渡しする定電圧回路と見ることが出来ます。

その定電圧回路を電圧増幅段と出力段の間の電圧差のある部分の結合に利用した回路を提案します。

SEPPアンプの出力オフセット電圧を無くすには、出力DC電圧を初段に負帰還するのが常套手段です。

しかし、そのためにはアンプがDCを伝達できる直結回路でなければなりません。

そこで、前述の定電圧回路の出番となるわけです。

2002/8/19

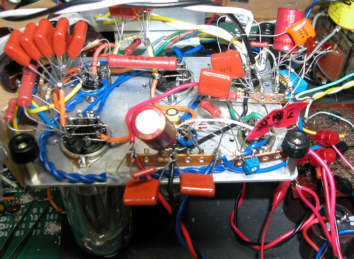

Mugendyne AMP実験回路2

飽きもせず実験を続けています。

入力信号にエラー電圧を加算するタイプです。

主アンプは2SK1529/2SJ200による1段だけのソース接地反転増幅回路で、2SC2856/2SA1191はバイアス回路、2SC3423/2SA1360はエミッタフォロワによるドライバーとなっています。

歪率 0.0007%(1kHz、8Ω負荷、1W出力)、出力抵抗は 0Ωでした。

2002/8/19

井出さんの回路を添削

フォールデッドカスコード風の回路ですね。

電流折り返しを定電流回路から抵抗に置き換えた回路にして、少し添削しました。

グリッド接地回路のグリッド電圧の基準点は、電流折り返し抵抗よりも初段管のプレート内部抵抗が低い場合はアースでよいですが、電流折り返し抵抗が初段管のプレート内部抵抗よりも低くて、グリッド接地回路のカソード内部抵抗よりも高いという前提で、グリッド接地回路のグリッド電圧の基準点を電流折り返し抵抗の方へ置きました。初段がプレート内部抵抗の高い5極管であれば迷わなくてスッキリします。

グリッド接地回路のプレート負荷抵抗の端は、上下とも出力管のプレート、またはカソードに同じように接続することが、上下対称動作の要ですので、取りあえずプレートの方へ接続するように直しておきました。

この方式の大きな問題点は、初段プレートとグリッド接地回路カソードを連結する定電圧回路に信号電流が流れるので、その定電圧回路の内部抵抗が影響することです。

2002/9/20

2002/9/22

カメさんに頂戴した32Ωのマッチングトランスを活用すべく、回路の検討をしています。

出力素子を何にするかも悩む所ですが、一応候補として2SJ18、6336B、EL509を上げています。

EL509の新型管が先日手元に届いたので、そのための回路を起こして見ました。

図の定数は実際に使う部品をモデルにしてないので仮の値です。

回路方式は絶対完全対称なクロスシャントプッシュプルです。

クロスシャントプッシュプルは出力管毎に独立した浮動電源を必要としますが、SEPPと同じように出力トランスの全巻線が開放されることなく出力管で制御できるので、トランジェント歪の発生がない点から、出力トランスを使用する場合に採用する価値のある回路と思います。

マッチングトランスに直流が掛からないようにするため、DCアンプ構成でオープンループゲインを高めました。

そのため2段の電圧増幅回路は定電流能動負荷としてあります。

EL509はビーム管ですがスクリーングリッド電圧の変化でプレート電流が変動するため、スクリーングリッド電圧の変化に合わせてコントロールグリッドのバイアス電圧を変化させるPSDC回路を使いました。

新型管EL509-2

中身はEL509ですが、概観が6550のような形になっています。

トップに出ていたプレートは3番ピンに来ていますから、電極のピン配列も6550等と同じです。

2002/9/24

PSDCによるバイアス回路のアイデアを一つ、したためておきます。

出力はCSPPになってますがDEPPにも使えます。

電圧増幅回路はこの際どうでもよいので、OPアンプ2個で差動出力を得るようにしました。

その差動出力にバイアス電圧を加算するため、R12

2002/9/25

PSDCのシミュレーション

6CA7の3結をモデルを使って下図の回路でDC解析しました。

Q1はPNPはトランジスタでエミッタは接地してあり、R1とR2で反転増幅器を形成しています。

このためVbの変動のR2/R1倍の電圧が6CA7のコントロールグリッドに加わることになり、プレートにはコントロールグリッド電圧のμ倍の電圧が発生します。

そこでR1/R2=μに設定しておけば、Vbの変動に等しい電圧がプレートに発生するようになるため、Vbとプレート電圧に電圧差が発生しないことでVbが変動してもIpには変化が起こらなくなります。

IsetはIpを任意の値に設定するための固定バイアス電圧をつくるためのもので、Vb=200Vの時、Ip=100mAとなるようにカットアンドトライで決めました。

IcはQ1の負荷となる定電流源です。

VAm1はIpを測定するための電流計で、Vbを0から400Vまで変化させた時のIpをグラフにしました。

この6CA7のモデルのμは事前のシミュレーションでIp=100mAの時、Vb=200V前後で8.8であることが解ったので、R1/R2=8.8に設定してみましたが、Vbの上昇に連れてIpが少し増加したため、R1/R2=8.6にした所、グラフに示す通りにIpの変化を無くすことが出来ました。

Q1のhfeがもっと大きければR1/R2=8.8に近付くと考えられます。

2002/10/8

2002/10/10

初段のゲートを接地するとは、下図のようにすることですね。

初段ソースフォロワの電源が接地されていれば、仰るように入力インピーダンスはきわめて低くなりますが、初段ソースフォロワの電源は出力段MOS-FETのゲートに接続されているので仰るようにはなりません。それとこの回路では動作しません。

ちなみに下図のように出力段をソース接地にすると出力からの帰還がかからないので、増幅度が無限大のアンプとなります。

この無限大アンプに下図のようにNFBを掛けることで増幅度が定まります。

上は反転アンプ、下は非反転アンプです。

このアンプの登場によって最早電圧増幅回路というものが不要になる画期的な回路であることをガッテンして頂けるでしょうか。

2002/10/11

井出さん↓これは素晴らしい、私には考え付かなかったです。それにどうしてこれでちゃんと動作するかさえ今の私には理解できません。

しかし私としては初段ソースフォロワと出力段MOS-FETのの接続関係を崩したくないので、間にβ回路を入れるこの回路は例外としたいですが、研究価値はありそうです。

2002/10/12

クロダさんマダマダだね。下の回路のように直さないと。

<img src="http://www.ne.jp/asahi/evo/amp/1d1c/kuroda.gif">

ベース結合差動回路の上の定電流回路は不必要ですから取り去りました。

ベース結合差動回路のバイアスは出力管のコントロールグリッド電圧から同相帰還することで安定した動作となります。

入力の対のトランジスタのベース側をコンデンサー結合にして直流抵抗を等しくすることで、直流バランスがよくなります。

出力管のスクリーングリッド電圧はB電圧と同じ方法で安定化するのがよいでしょう。

その際、倍電圧整流回路の中点の電圧を利用すれば、制御トランジスタの発熱を減らせます。

MacNontanさん推薦の本にも説明のあるOPA627/637がベース接地差動回路ということで741の系譜でしょうか。

クロダさんの意向が本心かは知りませんが、出力は望まないと云うようなことでしたので敢えて触れませんでしたが、

現状で出力管のコントロールグリッド・カソード間電圧が10V位になっていますから、Y-電圧を-30V程度にして、1MΩVRで出力管のカソード電圧を0か少しマイナスになるように調整すればフルスイング可能です。

更に出力を上げるなら、どうせ全段差動ではないのですから、出力管カソードの定電流回路を取り去ってB級動作にしましょう。

ただ、MJ 11月号の黒川さんの動作例のようにカソードNFBを掛けるには、このままの回路ではだめで、2段増幅かフォールデッドカスコードにしなければなりません。

何故かは各部分に発生する信号の電圧振幅を考えてみれば分かるでしょう。

2002/10/16

私の疑問点としましては,結局 アンプAM のひずみを減らすために

前段に アンプAE を持ってきてメジャーループNFBをかけるのと

どこが違うの?という点です.つまりアクティブなひずみの打ち消しとは

言えないのでは?と思います

その疑問は正しいです。AEの負荷インピーダンスが∞の場合にAEのゲインが∞となるから、メジャーループNFBをかけると歪のない増幅が出来るわけです。

しかし現実にはAEの負荷インピーダンスが有限であるため、この方式でムゲンダインは無理であることに血の巡りの悪い私も漸く気付きました。

仮にAEの負荷インピーダンスが∞でAEのゲインが∞である場合にはZDRの原理通りになります。

その説明のため下図のように井出さんの回路を描き写しました。

Q1の負荷インピーダンスが∞であるならQ1のゲインが∞であるため、ゲート・ソース間はバーチャルショート状態になっていて、Q1のVDGとVDSは等しいので、Q2のVGSがQ2の入力信号に加算されているように見えるでしょう。

もっと端的に変形すると、下図の私が以前に考えたボルテージミラー回路になるんですね。井出さんに諭される前に自分で早く気付くべきでした。

ボルテージミラー回路を思い出して、井出さんの説の通りベース接地回路の∞負荷が正しい解釈と思うようになりました。

Q2の手前に入力容量の小さいドライブ段を設けるとか、in側のインピーダンスを低くして相対的に充分Q1の負荷インピーダンスが∞と見なせるようにすることで原理に近い動作が得られるとは思います。

しかし今度は∞負荷を当てにしない別の方式を考えることにします。

2002/12/17

2002/12/20

差動アンプの定電流回路には電源リップルを排斥する効果があるので、電源のリップルフィルタを厳重にする必要など無いにも拘らず、それをしなければハムが出るのは回路設計が不適切 だからで、差動アンプのグリッド側が定電流回路をまたいで電源に接続されているために、プレートとグリッドの間に電源リップルを与えていることが問題と思います。

その点を改良した回路を下図に示します。

差動アンプのプレート側とグリッド側の間は、R1を通してC1に充電されたリップルの無い電源です。

GND電位は直流的には-Vc2と等しいが、交流的には+Vbに等しくなっています。

つまり、交流的には定電流回路で仕切られてクリーンな+Vbだけを基準に動作するわけです。

実際に組んでいないので図の定数が適当かは不明です。

D1は電源立ち上がり時にC1の充電を速やかにするためと、出力段のグリッドや定電流回路に過大な電圧が加わるのを防ぐためのものです。

D2は電源オフ時にC1を放電させるためのものです。

それでは皆さんよいお年を、さようなら。

2002/12/30

2003/1/11

2003/3/28

AOC

初段の反転入力側に入れようとすると、AOCの回路が少し複雑化する。

MJ4月号の回路は初段が5極管なので、スクリーングリッドにAOCの制御信号を与えるなら回路は複雑化しないが、+144V電源をアースに対して安定化する必要がある。

2003/4/22

シミュレーション制御方式バイアス回路

フォトボルをMOS-FETのバイアス電源とし、そのMOS-FETのドレイン電流を一定に保つことの出来るバイアス回路です。

MOS-FETにはVgsの温度特性があり、フォトボルも温度に対する特性変化があるため、個々に温度補償していては部品点数が増えて回路が複雑化するし、高い温度安定性は望めません。

最も理想的な制御方法はドレイン電流を監視してそれが一定に保たれるようにフォトボルのLED電流を制御するフィードバックループを形成することですが、ドレイン電流から信号電流成分を除いてバイアス電流成分だけを検出する必要があり、そのためには回路が複雑化します。

制御するべき主たるMOS-FETとフォトボルの回路と同じ温度特性を持つダミーの回路を用意して、信号電流を含まないダミー回路でドレイン電流を一定に保つフィードバックループ制御を行い、フォトボルのLED制御電流を主回路に与えれば、主回路のドレイン電流もバイアス電流成分が一定に保たれるだろうと考えました。

下図はその実験回路です。

主回路はPv2のフォトダイオードの出力電流をR2で電圧に換えてTr2のバイアス電圧としています。

それと同じ構成のPv1,Tr1部分がダミー回路で、Tr1のドレイン電流は定電流源の電流Id1と同じに保たれるようにTr3がPv1のLEDの電流を制御します。

Pv1とPv2のLEDを直列にしてあるため、主回路のTr2のドレイン電流もTr1と同じように制御されるわけです。

Tr1とTr2は温度条件が等しくなるように熱結合してあります。

R1でTr2のドレイン電流を調整して約0.2Aにセットしました。

この実験では、Tr1の2SK982とTr2の2SK2952の温度特性が同じでないため、Tr2の発熱によってTr2のドレイン電流が40%ほど増加しました。

Tr1をTr2と同じ2SK2952にすると逆に減少するので、2SK982と2SK2952の間のチップサイズのMOS-FETにドレイン電流一定となる適当なものがあるだろうと楽観してます。

2003/4/23

昨日の実験回路でTr1が2SK982でId1を15mA程度にすると多少の揺らぎはあるものの一定電流を保つようになりました。

ダミー回路に15mAも使うのは無駄なので出来れば1mA以下で使えるもの探したいです。

下図は金田式対称アンプへの応用例ですが、バイアス回路の直流抵抗が高いため、Tr2,Tr3のゲート側でAC成分が整流されるとバイアス電圧が狂う可能性があります。

ダミー回路でシュミレーションして制御するというこの方式は他にも利用できそうです。

というよりもそのような回路モデルは既に存在していたりして、皆様ご存知でしたら情報をお寄せください。

2003/5/1

スカラー波対策ラインアンプなんちゃって。

こんなことに感心を持ったり理解しようとすることに時間の無駄を感じつつ、電子回路のシンボルをお呪いのお札にしているので、スカラー波とは方向性を持たない電磁波であるらしいが、存在自体がウザイものの象徴なのかなと。

2003/6/7

大型Rコア出力トランスの活用法ということで考えてみました。

2つあるカソードNF巻線をシングルアンプでは直列にしてカソードNFに用いるのが常識的な使い方ですが、1つをカソードNFに用いて、もう一つをスクリーングリッド電圧のブートストラップに利用する回路を下図に示します。

ブートストラップによってカソードとスクリーングリッド間の電圧が一定に保たれるため、理想的な増幅動作が行われます。

カソードとスクリーングリッド間のコンデンサCSGは無くても構わなく然程重要でないかも知れません。

スクリーングリッドの最大定格内であればスクリーングリッド電源ESGをプレート電源EPと共通にすることは可能ですが、水平偏向出力管などは特にプレート電流を適当な値に設定するためには、コントロールグリッド電圧を深く−にしなければならず、カソード抵抗RKによる電力ロスが大きくなるので、ESGにEPと別な低電圧電源を備えるが必定。

さすれば、高いB電源から低いESGを得るために6C19Pのような低μの3極管を利用しては如何かと、ついでに下図のようにスクリーングリッドとコントロールグリッドの両方に信号電圧を与えることが可能となれば尚一層の理想的増幅動作が行われましょうぞ。

2003/7/11

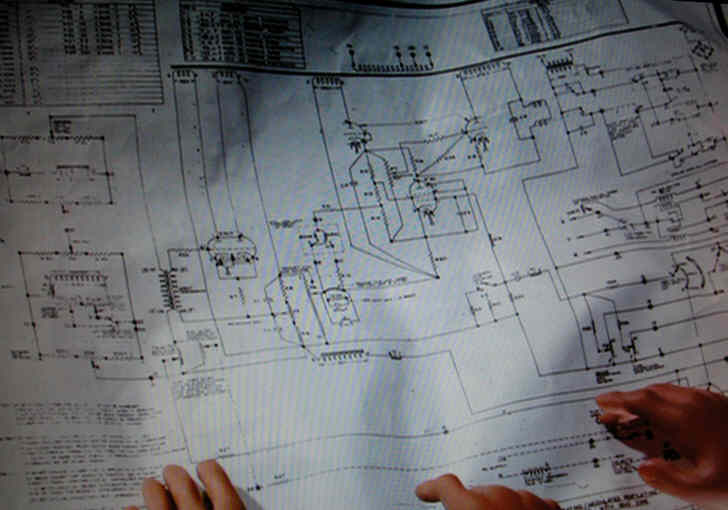

2065年に行ってサンダーバード2号の機内でブレインズが広げていたファイヤフラッシュ号の回路図を撮ってきました。

差動ではなくてグリッドは並列で、プレートがそれぞれに共通の出力トランスみたいなものに接続されている。

左の入力トランスに接続されているのがポテンシオメータならサーボシステムに違いない。

が、しかし、フェダーボリュームだとミクシングコンソール?いやそんな筈は。

サーボの信号系はACで、サーボの出力は油圧バルブを駆動すると考えたい。

これが該当部分。スパイが切断したケーブルは無視して、シールドが被せてある真空管はかなり寸詰りだからニュービスタの類かもしれない。

真空管ソケット周りの抵抗は5%級、ここだけリード線に絶縁チューブが使われているのは何らかの必要の処置だろう。

2003/8/23

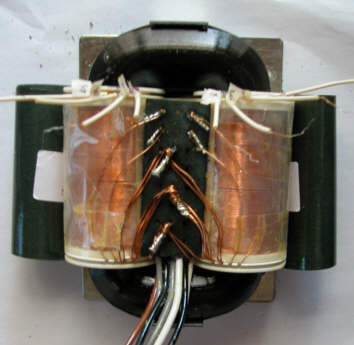

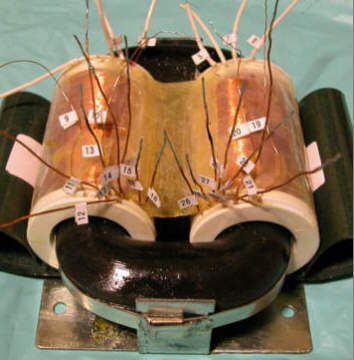

RW-40-5の改造

改造作業は巻線の引出し線が根元から切れたら取返しの付かないことになるので慎重に行うこと。

黒い外皮に2次側リード線の方からハサミを入れて切開すると、1次側巻線の引出し線とリード線の接続部分が拝めます。

尚、RAシリーズの電源トランスでは珪素鋼板のシールドが巻いてあるのでこうは簡単に行きませんョ。

リード線を取り去る前に復元を視野に、リード線と巻線の引出し線との関係をノートにメモしておくことを忘れずに、もし忘れそうならメモすることをメモしてネ。

私はバラシが得意なので、ちゃんと綺麗に捩りをほどいて取りましたけど。ぶきっちょでハンダ付を外すのが難しければハンダ付部分をニッパで切った方が良いと思います。

後学のために2次側の接続部分も拝見させてもらいました。

接続の様子から現状の巻線構造を読取ると以下のようです。

(プッシュプル使用)

巻線の巻始めが右と左で上下逆転しているのはリングコアに添って図示したからです。

プッシュプルの結合はコアの磁力線と2次側経由だけのようで、これはP1とP2のストレー容量による結合を避けるためでしょうか。

しかしDEPPのB級動作では出力管がカットオフした時に相当にスイッチングトランジェントを発生しそうです。

プレート内部抵抗の高い5極管やビーム管でその傾向が顕著に現れるため3結やUL接続にすることが無難で、これにカソードNFは効果ないように思われます。

既に試作検討済みのことかも知れませんが、1次側巻線を左右半々にブレンドしてはどうかと思いました。

それとカソードNF巻線が左右独立なので、初段に掛けるNFBの巻線として使用する場合は単独で使わずに、左右を直列か並列にして両方の信号を合算しないと不味いですね。

改造の方は今後の用途に合わせて、臨機応変に対応しようかと考えています。

取り合えず、巻線の引出し線に下図の様に番号を振りました。

引出し線番号と巻線との関係は下図の通りです。

番号1-2と7-8、3-4と5-6の巻線抵抗が等しいので、CSPPの場合は以下のようにするのが良いだろうと思います。

CSPPは番号1-8と3-6の巻線が交流的に並列なので、1次側インピーダンスはDEPPの1/4になります。

プッシュプルの出力管が共通の巻線に並列接続されているので、B級動作で片方の出力管がカットオフしてももう片方の能動状態の出力管がスイッチングトランジェントを吸収しますから、出力トランスにプッシュプルの結合を要求しない所はCSPPの長所です。

2003/9/1

上図のマッキントッシュ風CSPPにRW-40-5を使用する場合、1次側の接続を下図のようにすると1次側インピーダンスは2次側の8Ωと4Ωに対して1250Ωとなります。

(この図は、同じ巻数、同じ直流抵抗の巻線が左右対称)

最大出力50W程度を得るためには、出力トランスの1次側インピーダンスが1250Ωの場合に、プレート電源電圧が400V〜450Vは必要になり、ドライブ段にも対アースでそれ以上の信号電圧振幅が要求されます。

下図のように2次側巻線の並列接続を直列接続に変更することで、1次側インピーダンスの1250Ωに対して2次側は32Ωと16Ωになるため、2次側の32Ωに8Ωを負荷、または16Ωに4Ωを負荷することで、1次側インピーダンスが313Ωとして使えるようになります。

ただし2次側巻線の直流抵抗は4倍に増える。

(この場合KNF卷線と0-4Ωの卷数が等しいため並列接続した)

出力トランスの1次側インピーダンスが313Ωならば、プレート電源電圧が250V〜300Vで、最大出力50W程度が得られそうです。

2003/9/4

回路案です。

特定の真空管を想定しているわけではないので、定数は確定的なものではありません。

真空管仕様では電圧配分がかなり厳しいので、出力管以外を半導体にして、出力管のG2電圧をツェナーダイオードで調整するのが現実的かと考えています。

2003/9/8

パソコンを作りました。

と言っても出来合いのパーツをケースに組み込んでコネクタを接続しただけのことですけど。

ケースの加工と放熱用アルミブロックの製作がしんどかった。

場所をとらないB5サイズのアルミケース、ファンレスなのでハードデスクがたまにカタッと鳴る以外に音はありません。

これから秋の夜長、静かに時を過ごすことができそうです。

マザーボードは VIA EPIA ME6000 (170mm×170mm) http://www.viatech.co.jp/jp/vpsd_jp/products/epia_M_spec.jsp

HDDは2.5インチ流体軸受け

真空管アンプのシャーシ下に組み込むつもりが、使い勝手が悪そうなので予定変更してこのようなものとなりました。

真空管アンプの方は構想がまとまらずお流れです。

2003/10/4

RW-40-5の改造報告

卷線の引出し線に管理し易いように番号をつけました。

奇数の番数が卷始めでそれに+1した番数がその卷線の巻終りとしました。

2次側は芯側から若い番号をつけました。

2次側の引出し線は左右10本づつあるので、左右対称の卷線を番号の1桁目が同じにしました。

引出し線に番号タグを付けたところ

改造前の接続

改造後の接続

KNF卷線は卷数が少し多いのか発生する電圧が0-4Ωよりも高くて、0-4Ωに並列接続すると短絡電流が生じたので、どこにも接続しないで開放してあります。

引出し線番号14,15,24,25の接続点が4Ωのリード線を接続する端子となりますが、4Ωは必要ないのでリード線の接続はしてありません。

切り開いた所をガムテープで修復して改造完了。

周波数特性 (信号源インピーダンス100Ω、入力3V、2次側8Ω負荷)

元の仕様の卷数とインピーダンスの割合では1次側1250Ω:2次側32Ωなのですが、2次側に8Ωを負荷することで1次側312.5Ωとしますので卷数が元の仕様に対して2倍となり、それが特性にどう影響するか気になる所ですが、インダクタンスが増えたことで低域は10Hzでもほとんど低下しませんし、高域は元の特性と大差ないようなので周波数特性には問題ないようです。

2003/10/22

EL509 CSPPアンプ

改造した出力トランスを使うためのアンプを実験中です。

アンプ回路

電源回路

回路は実験中の暫定的なものです。

EL509は100W以上の出力が可能ですが、出力トランスの能力から最大出力60WとなるようにB電圧を控えました。

EL509のG2は無信号時100V程度で、これにG1と同じ信号電圧を加えるようにしてあります。

7044のバイアスに電源電圧の変動分を与えることで、電源電圧の変動によるEL509のアイドリング電流の変化を抑えました。

7119と7DJ8の起用はヒーターウォームアップの遅さで立ち上がり時の耐圧オーバーや過大電流の発生を防ぐ目的ですが、万全を期するために遅延リレーでB電源に電流制限抵抗を入れることを検討中です。

ヒーターバイアスはヒーター・カソード間耐圧をクリアするために取った苦肉の策です。

EL509のアイドリング電流は1球当たり0.1Aに設定。

最大出力60Wは低域30Hzまで可能で、20Hzでは波形が崩れてしまいます。

高域-3dBは150kHz位、

出力インピーダンスは1Ω弱、

残留ノイズは0.1mV以下、

歪率は1W 1kHzで0.04%位ありますが2次歪成分が主なので、ACバランス調整で減らすことは可能と思われます。

2003/11/16

DC成分サプレッサ

MJ12 月号の『AC電源のDC成分サプレッサーで電源トランスのウナリ防止』でDC成分が抑えられる仕組みが解りません。

DC成分サプレッサの回路は下図のようになっています。(DC成分の極性は任意)

シリコンダイオードの導通開始電圧以下のDC成分はブロックされるから、ダイオード2個直列が双方向に入るので1.2V未満のDC成分はブロックすると書かれてます。

AC100Vが無ければそうですけど、DC成分とAC100Vが加算されている場合は、ダイオードの電圧を引き算しても、正負の電圧振幅の差はDC成分に等しいままでしょう。

もしかして、ダイオードにDC成分をキャンセルするバイアス電圧が発生するのでしょうか。

2003/11/16

DC成分サプレッサ

波形を描いて考えて見ました。

下図上側は+DCが加算されている電源波形で、赤と青の水平線の間がダイオードで切り取られる部分です。下側はダイオードを通過した波形です。

ダイオードで切り取られる面積が+側の方が幅が広い分だけ大きいため、面積的に見るとバランスがよくなる方向に接近しているからDC成分が減っていると解釈できます。

この理屈の通りなら、ダイオードでDC成分をブロックするのとはニュアンスが異なるようです。

このような回路でシミュレーションしてみました。

Rを1Ωから0.1Ωに変えてもDC電流成分はあまり変化しないけど、LでAC電流を変えるとDC電流成分も変化します。

下図のようにブリッジダイオードに大容量電解コンデンサを接続するとDC成分ストッピングという、サプレッサより一段高い上の機能をもたせることが出来そうです。

実際にはCと並列にRを接続して、Cに蓄積されるDC電圧を放出するためと、トランスのL分との共振をダンプするために必要です。

積極的に電源周波数に共振させると歪の少ないクリーンな波形に整形できます。

2003/11/19

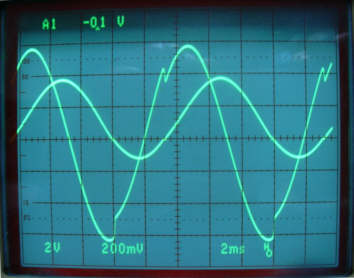

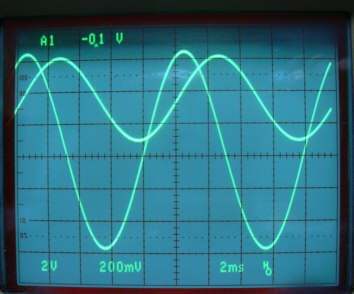

DC成分サプレッサの波形写真

キ村さんから、実験した写真を頂いたので掲載します。

fig2とfig3を比べるとVfの効き方がよくわかります。

fig1:DC=0V ダイオード-GND間の電圧(振幅の大きい方、2V/div)と、R両端の電圧(振幅の小さい方、200mV/div)

fig2:DC=0.4V

fig3:DC=0.4V ダイオード短絡。

DCサプレッサのシミュレーション

下図の回路でDCサプレッサをシミュレーションしてみました。

AC電源は50Hz正弦波で280Vp-p(約100Vrms)です。

ダイオードは順方向電圧Vf=2Vでスイッチする理想素子で単純化してあります。

回路の抵抗分は無視できるように1mΩとしました。

上のグラフはL=0.1H、Vdc=1Vの場合です。

黒色の波形が電流で、DC電流の値はAC成分の振幅の中心なので約3Aです。

赤色の波形はダイオード両端の電圧で、電流のゼロクロス点で導通方向が切り替わることが分かります。

青色の波形はL両端の電圧ですが、1つのグラフに他の波形と重ねて表示するため、振幅を1/10に縮めてあります。

Lの電圧はVac+Vdc-Vfとなっています。

グラフ上の丸囲いしてある部分にはダイオード両端の電圧が切り替わる際に発生する不連続な乱れがあります。

ダイオード両端の急峻な電圧変化はLに吸収されるため、電流に乱れは発生しません。

下のグラフの赤色の波形はL=0.4H、青色の波形はL=2.4Hの場合で、他の条件は上と同じです。

これはLによってDC電流が変化する状態を示すものです。

DC電流はおよそ、L=0.4Hの場合750mA、L=2.4Hの場合110mAとなっています。

下のグラフはL=0.4Hで、Vdcを変化させた状態です。

赤色Vdc=1V、緑色Vdc=0V、青色赤色Vdc=-1V

Vdcに比例してダイオード両端電圧のデューティ比が変化していることが分かります。

ダイオードがVdcに比例したデューティ比で導通する間に、その間の電流をIとすると、ダイオードはVf・Iという電力を吸収しています。

デューティ比はVdcによって変化しますがIによっては変化しないので、Iが大きくなるとDC電流が拡大します。

2003/11/23

DC成分リムーバ

抑制などという手緩いことではなく、除去することを考えてみました。

簡単には下図のようにコンデンサ結合とすることですが、大容量の無極性コンデンサを必要とします。

下図は電解コンデンサにダイオードでバイアス電圧を生じるようにした回路です。

並列の抵抗は電源トランスのインダクタとの共振をダンプするためのものです。

下図は電源電圧からCRフィルタでDC電圧成分を検出して、同じ電圧をDCアンプによって電源トランスの入力電圧に加算する方法です。

2003/12/8

突入電流防止機能付きDC成分サプレッサー

突入電流防止回路とDC成分サプレッサーを一体化したものを作ってみました。

電源トランスとAC電源の間に装着して、電源ON時及び瞬断後の突入電流を防ぐことと、DC成分を減らすための装置です。

10W47Ωは突入電流を防止する電流制限抵抗で、電源オン時にはこの抵抗を介してAC電源から電源トランスに電流が通ります。

RT2からCT2へ充電される電圧がTR5の閾値を越えるとTR5がONし、AC電源から電源トランスへの電流は電流制限抵抗をパスして、ブリッジダイオードを介してTR5に通るようになります。

TR1〜TR3は電流制限抵抗両端の電圧によって電源トランスの電流を検出しています。電流がある場合はCT1の電圧をTR4の閾値以下に下げていますが、瞬断などで電流が無くなるとRT1からCT1へ充電される電圧がTR4の閾値を越えてTR4がONし、フォトカプラを介してCT2を放電してTR5をOFFし、電流制限状態にします。

DC成分サプレッサーが目的のブリッジダイオードをACスイッチのMOS-FETを1個で済ますことと電流検出に利用したことがこの回路の特長です。

数センチ四方の大きさに作れるので筐体内の僅かなスペースに組込むことができます。また常時ACに接続していても電力消費は僅かなので外付けアダプターとしても使えます。

2003/12/9

> フォトカプラを使うなら、一次側を負電源で動くようにすれば100kと1μの充電電流が逆向きにできて、対称性が高まるってのはどうでしょう?

電流が少ないのでこだわり過ぎかと思いますけど、沢山普及した場合のことを考えるとあながち軽視できないので、そのアイデアを頂戴して回路図を描き直しました。

マッチ箱サイズにモジュール化して、電流制限抵抗は外付けにする考えです。

2003/12/10

> もう一点気になるのは,ZNRのデータシートを見ると「151」はAC95Vmaxとなっていることです.

> ここは,「201 or 221」にすべきではないでしょうか?

あ、そうでしたか、手元にあったのをデータも見ずに使っていました。早速変更致します。

それからトラ技1月号の定番エレクトロニクス回路からコンデンサの直列リアクタンスを使えば発熱を避けられるというのを、部品点数が増えるし高調波が心配ですけど取り入れてみました。

2003/12/14

フォトボルを使うことで部品点数を減らしました。フォトボルのLED電流でタイミング設定できますがLED電流が電源電圧変動を受けないように対策が要ります。それよりフォトダイオードの最大出力電圧が一定なのを活かしてタイミング設定はCRで行いました。

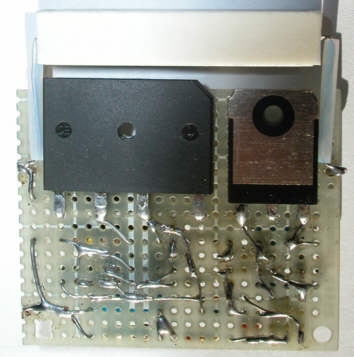

バラックだったのを実用になるように基板に組んでみました。

いざ部品はと見ると

オーディオ用のブランド品しか持ち合わせがなく、改まって組み立てしようとすると適当なパーツがなくて苦労します。

それでも実験材料の残りとか、ジャンク品の得体の知れないようなもまでかき集めると、買い足しに出かけずとも作れてしまうのは、無駄に喰った年季の賜物でしょうか。

プリント基板を起こすなら表面実装部品を使いより小型に作りたい所です。

しかし最早歳のせいか老眼になってきて拡大鏡なしでは作業ができないのが辛いです。

基板の大きさは57×47で、ゆったり目に作りました。電流制限抵抗まで含めた全体の大きさは57×61×15です。

下の写真はオシロで見たIN-COM間とOUT-COM間の電圧波形です。

垂直軸 上の波形:IN-OUT間の電圧 50V/div、下の波形:OUT-COM間の電圧 100V/div

水平軸:100ms

[写真1] 60W電球

[写真2] Rコア電源トランス使用パワーアンプ

波形の変化から見ると電流制限している時間は300〜400msになっています。

電球に使用しても突入電流が抑えられるので寿命が延びる効果があると思われます。

2003/12/29

SuperSIT

真正超SIT(Ver.1)の回路

ダーリントン超SITの回路

真正超SIT(Ver.1)では入力信号電圧Viのμ倍の電圧がVds1となるのに対して、

ダーリントン超SITではViからMOS-FETの入力信号電圧Vgs2を引いた電圧Vgs1のμ倍の電圧がVds1となるため、

MOS-FETのゲインが高ければその入力はバーチャルショート状態でVgs2の発生が小さく、真正超SIT(Ver.1)と同様にViのμ倍の電圧がVds1となるが、

MOS-FETのゲインが低いとVds1にはMOS-FETの特性の影響を受けた電圧が発生することになり、SITだけの純粋な電圧増幅特性というものが損なわれる。

真正超SIT(Ver.1)でも出力電圧VoはVds1+Vgs2であるから、VoはMOS-FETの特性の影響を受けるが、一般にVds1に対しVgs2は比較的小さいので、その影響は少ない。

2004/1/24

UN24/UN07の接続

使ったことがありますけど、資料を紛失してしまったので詳しいことは分かりません。

写真のようにUN24は外側から対称にDGSで真ん中はNCです。

UN07は印刷面から見て左からDGSです。

接合型FETなのでドレインとソースが逆でも動作します。

確かUN24とUN07は同じチップなので特性は同じと思います。

最大規格はVDGO=100V、ID=50mA、UN24のPD=250mW、UP07のPD=500mW、

gmは小さく5mS以下ではなかったかと、ドレイン電流のQポイントが1.5mAだとか、

Idssはランクによって違い、写真のDランクは10mA前後流れます。

UN24は2つの独立したチップで構成されているのでペアバランスのよくないものもありました。

1978年から1979年ごろの短い期間に流通していたので、その頃の雑誌に規格表等があるかも知れません。

UN24は初め高価でしたが、その後半額以下になったので買ったことを覚えています。

2004/1/25

このケースのためのアンプを製作しようと思っています。

ケースは上部が中央から割れて左右に開く構造です。

蟹の鋏の様でもあり、ゴッホの絵の跳ね橋の様でもあり、私はランボルギーニ・ミウラの前後カウルのオープニングなんですけど、イメージするもので人それぞれの個性が出ますね。

以前に一庵さんからご提案頂いた縦型真空管アンプの具現化に努めました。

側面から見て、ケースは若干オーバースクエアですが、真空管が立たる全容は縦型と呼べる範疇と思います。

材料は2mm厚アルミ板です。このためホーザン板金折り曲げ機(K-130)を購入しましたので、その使用感を書きます。

2mm厚にはまったく歯が立たたず、谷折側に板厚の半分位まで電動丸鋸でスリワリを入れて折曲げました。

折曲げ機のハンドル取付け部分の溶接が片面しかしてないため、すぐに変形して折り曲げ板とベースの隙間が広がってしまったので、修正後両面をアーク溶接して強度アップしました。

シャコ万を併用しましたが、それでも使っている間に押さえ刃の中央が引っ込んで湾曲に変形してしまいました。

幅広の厚物は無理みたいです。

ちょっと頑丈そうな↓こんなのだったら苦労しなかったかも、でも重いのが難点。

http://sk-world.com/japanese/Japanese/machine/3-in-1J.html

http://sk-world.com/japanese/Japanese/machine/HandBrakeJ.html

2004/1/29

UN24の特性

2004/3/7

このような回路になるのでしょうか。

出力管V3のプレート電圧が下がり切ると帰還管V1のカソード電圧がそれより低い電圧になるわけで、この回路のV1のカソードに発生する信号電圧の振幅でV3をフルスイングするのは難しいですから、下図のようにR8でV3のG1に+10〜20Vのバイアスを掛ければ良いでしょう。

カソードフォロワと出力管を直結にしてV3の

2004/3/14

クロスシャント位相反転回路の改良

下図は基本的なクロスシャント位相反転回路の模式図です。

信号注入側の出力の方が出力電圧が若干大きく、バランスに問題があります。

その点を改良するため、下図は差動回路の上にクロスシャント位相反転回路を積み重ねた回路です。

何のことはないカスコード回路として動作しますが、普通のカスコード回路より若干ゲインが大きいです。

クロスシャント位相反転回路のカソード側が低インピーダンスでないとクロスシャント位相反転回路にゲインが発生しないので、下図のように差動回路をSRPP回路にしてみました。

上図は模式図で、実際的にはバイアス電圧を適正にするための工夫が必要です。

SRPPではカソードフォロワほどインピーダンスが低くないので、クロスシャント位相反転段のミラー効果で高域特性が良くありません。

下図は差動回路の出力をカソードフォロワで受けて低インピーダンスでクロスシャント位相反転に信号を与える回路です。

シミュレータでは図の部品定数で、差動ゲイン60dB、高域-3dBの周波数2.7MHz、最大出力電圧800Vp-p以上の性能となりました。

2004/3/16

正しくカソードフォロワで受けるためにブートストラップコンデンサをクロスして接続しました。

クロス接続にするとゲインが下がり、-3dB点が上がりますが、元の接続でもゲイン0になる周波数は同じです。

元の接続でも、差動回路の6DJ8のプレート内部抵抗がプレート負荷抵抗の100kΩより低いので、次段の6DJ8は実質的にカソードフォロワに近い状態です。

しかしプレート内部抵抗より低いプレート負荷抵抗にした場合では、カソードフォロワではなくプレート負荷抵抗に発生する電圧のgm倍のプレート電流を流すだけの動作になるので、その電流変化をクロスシャント位相反転回路はそのまま上に向けて伝達するだけで、そうなればフォールデッド・カスコード回路です。