一日一回路

№1 シンプルなボルテージ・フォロワ(2001/2/6)

OPアンプとMOS-FETによるパワーブースターで構成するボルテージ・フォロワである。

OPアンプの電源は定電流回路で与えられ、その電圧はツェナーダイオードで安定化される。

同時にそれはコンプリメンタリーMOS-FETソース・フォロワのゲートバイアス電圧となる。

MOS-FETはVGSが高くGmが高いことが望ましく、OPアンプはレールtoレール入出力型を使う。

№2 シンプルなボルテージ・フォロワ(2001/2/7)

2段エミッタフォロワによるボルテージ・フォロワである。

既存の回路では2SA1190のコレクタは-電源に、2SC2856のコレクタは+電源に接続するが、この回路は出力に接続してコレクタ電圧をブートストラップしている。

2SC4793/2SA1837の無信号時のコレクタ電流は、2SA1190/2SC2856のコレクタ電流に比例する。この回路でそれは電源電圧によって変わり、±10Vでは0.1Aとなった。

1kΩを定電流回路にすれば、電源電圧に関わりなく2SC4793/2SA1837の無信号時のコレクタ電流を設定できる。

2SA1190/2SC2856のコレクタ電流によって2SC4793/2SA1837のコレクタ電流の最大値が制限されるため、負荷が低いほど最大出力電圧が減少する。この回路は8Ω負荷でクリップする出力電圧は10Vp-p(1kHz)だから、ノンクリップで1W以上は出る。歪率は0.29%(1kHz,1W)程度、2SC4793と2SA1837のベース間を220μFで結合すると0.075%まで下がり、最大出力電圧も12Vp-pまで増加した。出力抵抗は0.22Ω。

№3 シンプルなプッシュプル回路(2001/2/24)

プッシュプル回路の共通カソードにチョークコイルを挿入すると、AF信号に対して差動回路として働くため、位相反転回路を回路を必要とせずにプッシュプル動作する。

№4 並列給電SRPP(2001/2/26)

SEPP回路には並列給電型があるが、SRPP回路では見たことがないので考えてみた。

何か複雑な回路を予測していたが、拍子抜けするほどシンプルな回路になった。

V1の下段はカソード接地動作で、上段のV2は下段のプレート出力電圧をカソードフォロワで出力する。

V2のカソード電圧は出力トランスのコイルの直流抵抗分による電圧降下だけアースに対して高くなるので、V2のグリッドバイアス電圧は、V1のそれよりも高くしなければ、V1とV2のプレート電流は等しくならず、出力トランスが直流磁化されてインダクタンスが低下する。

そこでV1とV2のプレート電流が等しくなるよう、RBLでV2のグリッドバイアス電圧を調整できるようにした。

真空管の代わりにSITを使用しても面白いだろう。

№5 ダイヤモンド差動(2001/3/3)

差動回路は共通カソードの定電流回路に拘束されて、片側がカットオフするともう片側が電流飽和してしまうことで、A級動作範囲でしか使えずパワーが取れないため、山水のダイヤモンド差動を真空管回路に応用してみた。

A級動作範囲では下側の2球が一緒になって定電流回路として動作するので、上側は差動回路として動作する。

差動回路の片側がカットオフする入力では、下側は定電流ではなくなり上側と同じ電流が流れるので、上側は電流飽和することなくB級動作に移行できる。

№6 2球シングルアンプとトリプルアンプ(2001/3/3)

2球シングルアンプの上側のカソード接地アンプと出力トランスを並べ替えると左図のようになる。

これは右図のように、の2つの3極管がμが2倍の1つの3極管と等価である。

トリプルアンプの2つの3極管はμが2倍の1つの3極管と等価である。

左図は3極管が下側になる場合で、右図は上側になる場合を示す。

№7 積木細工位相反転回路(2001/3/5)

知らない方のために積木細工回路とはこんな回路です。

基本的にはカスコード回路の2段縦列(カスケード)回路による位相反転回路です。

つまりインバーターの2段接続で、1段目から反転出力を、2段目から非反転出力を取り出す方式です。

2段目の出力レベルを1段目と等しくするためR1で調整するようになっています。

こんな回路もアリかなって軽い感じで作ったような気がします。綺麗な回路とはいえないし、何か特筆すべき点はあるでしょうか

№8 積木細工位相反転回路トランジスタ版(2001/3/6)

Q1のIcの変化でQ2のVBEが変化します。Q1とQ2のIcの変化量は同じだから、Q1とQ2のVBEの変化量は同じです。

Q2のVBEの変化はQ3のVBEの変化となり、これはQ1のVBEの変化とは逆相で同振幅であるから、Q3とQ4のIcの変化はQ1とQ2のIcの変化と逆相で同振幅となります。

素子の特性がそろっていれば無調整で反転出力と非反転出力を等振幅で得ることができます。

トランジスターではベース電流の影響があるので、その分精度が落ちますが、MOSFETなら完璧で、IC化に適しています。

真空管回路では見栄えのしない積木細工でしたが、トランジスターで構成すると偉くスマートになってしまいました。橋本順次さんは既にこうなることを予見していたに違いないと思います。

№9 Tr積木細工位相反転回路の実験(2001/3/7)

実際に回路を組んで実験してみました。

直流電流安定性を上げるためエミッタ抵抗を追加しまし、出力のDCバランスを取るためVRで調整できるようにしました。

トランジスタはVCEの飽和電圧の低いタイプを使用する必要があります。LEDは赤色を使いました。

1kHz

1Vrmsの出力で歪率を測定してみたら、1段目の反転出力側は0.13%ですが、2段目の非反転出力側は0.07%と半分近く低くなりました。

これはVBE-Ic特性の非直線性が1段目と2段目の間で打消されているからです。

№10 ゲイン1低歪反転アンプの実験(2001/3/10)

積木細工位相反転回路の実験で、なぜ2段目の出力の歪が1段目の出力の歪より低くなるのかは、まだ理論的な解明ができてませんが、Q1のコレクタに入力と逆相で等振幅電圧が発生することは明解です。

そこでQ1のコレクタ電圧が実際にどの程度の歪率かを下図の回路で確かめてみました。

1Vrmsの出力で100Hz 0.0037%、1kHz 0.0018%、10kHz

0.0020%となりました。

入力コンデンサーに220μFと大きな容量のものを使ってますが、この容量が小さいと低い周波数の歪率が悪化します。

これは入力コンデンサーの容量が小さいと低い周波数では入力側のインピーダンスが上昇するために、ベース電流による影響が発生すると考えられ、FETを使用すれば容量には作用されなくなると思います。

この実験ではトランジスタを無差別に使用したので、ペア選別するならばもっと歪が減るかも知れません。

また歪成分は第2高調波が多いのでコンプリメンタリプッシュプルにすれば更に低歪化が可能になると考えます。

このアイデアは私の製作したD-NFBアンプの初段に持って来いで、アイデアのきっかけを与えてくださったtaroさんに感謝いたします。

№11 カスケード歪打消アンプ(2001/3/10)

ラジオ技術4月号にユニークなアンプが掲載されました。

一見SRPPのように見えますが、何だろうこれは?

下側のV1、T1、B1で構成される回路はカソード接地増幅回路です。

上側もV2、T2、B2で構成されるカソード接地増幅回路で、その入力にはT1に発生する下側の出力電圧をVRで絞って与えています。

従って下側と上側は2段縦列(カスケード)接続となっています。

T2の1次側はT1と逆相接続で、2次側がT1と同相になるように並列接続されているので、下側と上側の出力はプッシュプル合成されます。

下側と上側が同一特性であれば、下側で発生した歪は下側と逆相で動作する上側の歪によって打ち消され、上側の出力は無歪となるだろうという発想でこの回路ができたそうです。

そのため上側出力だけの歪を測定したが、上側と下側の出力を合成した場合より大きかったと記してあります。

その際は下側と上側の動作条件が同一となるように、下側出力には上側出力と同じダミーロードを接続して、VRで歪の最小ポイントに調整した状態です。

上側と下側の出力を合成する接続によって、上側には出力からの正帰還が掛かることがキーポイントではないかと私は直感しましたが、ZDRのようなフィードフォワード回路のようにも感じられ、果たして本当の所は何なのか興味深い回路です。

しかし、どうしてこうもラジオ技術にはユニークな回路が登場するのか、パイオニア精神で自ら思考して回路設計する人が着いていることがこの雑誌の底力と思います。

№12 アースループ(2001/3/11)

MJに先月号に続いてアースについての記事が載っている。

ステレオアンプでは入力ケーブルによってアースラインにループができるのは避けられないが、私は図の水色部分のようにアースループの面積が最小となるように工夫することで対処している。

№13 フィルターコンデンサーの配線(2001/3/11)

MJ4月号のアースについての記事の中でAの回路図が載ってましたが、この配線ではブロックコンデンサーと電源トランス間の配線インピーダンスに、ブロックコンデンサーを充電する時にリップル電圧が発生し、それが電源電圧に乗ることになります。

電源トランスは電流を伝達する電線の一部に過ぎないのに、電源そのものと勘違いしているのかも知れません。

Bのようにインピーダンスの最も低いブロックコンデンサーの端子部分から枝分けするように配線するのが正しいと考えます。

№14 フィルターコンデンサーの配線(2001/3/13)

石坂氏が大声でいわねばならないとまで書いてあることは、電源トランスとコンデンサー間の配線を最短距離で結ぶことと、下図のようにリップル電流をシャーシに流してはならないことと私は解釈しました。

コンデンサーの端子側ではなく電源トランス側をアースとするべき理由については書かれてないので、石坂氏はチューブラ形コンデンサーを使った配線を前提にしているのではないかと思います。

№15 正しい並列給電SRPP(2001/3/18)

このカソード接地とカソードフォロワによる回路は、V2のグリッド・カソード間に信号電圧が生じないためSRPPとして動作しない。

V1のプレート電流からV2のドライブ電圧を発生させるためのRpが必要なのだ。

№16 ラ技4月号黒田さんの位相反転回路(2001/3/24)

上側が反転増幅器で、下側が非反転増幅器です。

それぞれの出力電圧について考えてみると、

②式から非反転増幅器のVo2はVin以上にならないことが解ります。

またA2のゲインが無限大ならばR3,R4に関係なくVo2=Vinとなります。

R1=R2,R3=R4の場合③,④式のようになり、A1=A2であれば、その大きさに関係なく

-Vo1=Vo2が保たれます。

次に入力抵抗について考えてみると、

R1=R2=R3=R4=RとしA1=A2である場合、入力抵抗はRのままで変化しません。

№17 黒田位相反転回路によるアンプ(2001/3/25)

黒田さんの位相反転回路を応用したアンプ回路を考えてみました。

V1,V2,V3,V4が位相反転回路でR1=R2=R3=R4となっています。

V1,V3と,V2,V4のプレート電流はQ1,Q2のフォールデッドカスコードによって出力管V5,V6のグリッドに伝達します。

V5,V6は交差型カソードフォロワ回路で、Vp1,Vp2は浮動電源です。OUTにセンタータップ付きマッチングトランスをつなぎ、センタータップをアースに接続するならR7,R8は不要です。また更にVp1,Vp2のプレート間にセンタータップ付きチョークコイルをつなげば、センタータップとアース間に電源を接続する、クロスシャントPP方式できます。

この回路の電圧ゲインは2なので、前段に電圧増幅回路が必要になります。

№18 無歪増幅回路(2001/4/2)

原理的に歪を発生しない電圧増幅回路のアイデア

条件は、

Q1とQ2が特性の揃ったペア素子で同じ温度条件となるように熱結合されていること、

R1=R2であること、

高精度のカレントミラーによって

I1=I2となっていることです。

このように(R3+R4)/R3のみによって電圧ゲインが決定され、非直線性歪を持つVBE成分を含まないため、無歪増幅ができる。

№19 無歪増幅回路の実験(2001/4/7)

無歪増幅回路を実際に組んで実験してみました。

原理図のR1,R2に相当する1kΩは選別して4桁まで同じ抵抗値の物を使用してます。

Q1,Q2の動作条件を等しくするためカスコード接続しました。

出力はJ-FETによるソースフォロワとしました。

カレントミラーの伝達係数を100Ω半固定抵抗で調整して歪率を最小にできるようにしました。

その結果、歪率は1kHz 8Vp-pで0.0015%、歪成分は第3高調波とノイズです。

各部の電圧を回路図中に記入しておきました。

№20 無歪増幅回路の実験(2001/4/8)

カレントミラーで方向転換せず上に積み重ねる方法を考えて、下図の回路で実験してみました。

入力電圧は2SK30と2SA1015で構成される一対のトーテムポール回路によってV-I変換され、この電流はその上側にあるトーテムポール回路に与えられ、上側トーテムポール回路の電流が下側トーテムポール回路の電流と等しくなるように、2SK117,2SC4793を介したフィードバック系によって制御されます。

よって上下トーテムポール回路のgmが等しい場合、歪のない増幅が可能になります。

上側トーテムポール回路に100ΩVRを入れて上下トーテムポール回路のgmのバランスを調整できるようにしました。

歪率は出力8Vp-pで、100Hz 0.00055% 1kHz 0.0006% 10kHz 0.0014% と極めて低くなりました。

№21 アイソレーションアンプ(2001/4/15)

無歪増幅回路の実験から誕生したE-Cloneというアーキテクチャをアイソレーションアンプに取り入れてみました。

4/7の回路のカレントミラーの部分をフォトカプラに置き換えることでアイソレーションアンプができると考えました。

この回路ではマスター側の2SK30のドレイン電流と等しい電流がスレーブ側の2SK30のドレインに流れるように動作します。

VR10kΩは2つのフォトカプラの特性差を補正するためのもので、入力0の時に出力0となるように調整します。

マスター側とスレーブ側の2SK30の特性が等しく、尚且つ温度条件も等しければ、歪のない出力が得られる筈ですが、フォトカプラTLP521の動作速度が遅く、ノイズが多いため測定データは酷いです。

ノイズは 5mVで、歪率は出力8Vp-pで、100Hz 0.02% 1kHz 0.12% 10kHz 0.5% でした。

オシロスコープで100Hzの歪成分が殆どないように見えたので、ノイズ成分が少なければ歪率は0.00台になると思います。1kHzと10kHzでは3次歪が主成分です。

№22 超3結FX(2001/4/28)

かつさん、お待たせしました。リアクションがちっともないのでイライラしていませんでしたか。

皆も私のコメントを待ってから反応しようと後出しジャンケンを決め込んでいたのかも、それとも楽しみなGWの準備でそれどころではなかったとか。

先週からプリンターが故障(原点位置確認できない)してしまい、そんなわけで普段ならプリントアウトして紙の上でじっくり検討するところですが、それができずディスプレイ上だけの浅い見解になりましたことをご容赦ください。

3極管によるドライブ段で負荷を出力に接続してあると3極管の内部抵抗を介してNFBが掛かりますから、帰還ループに3極管を入れるという超3結のスタイルを踏んでいるので、拡大解釈すれば超3結といえなくもないですが、この効果をアグレッシブに引き出して、より理想的な状態になるように回路設計するところに超3結的精神というものがあるように思います。

ドライブ段が差動回路になってますが、出力管のグリッド・カソード間電圧を0Vまで振るためには、差動回路をカットオフするまで動作させなければならず、歪の点で問題です。

ドライブ段のプレート側を定電流で引っ張ってやるとか、プレート負荷抵抗にDC電圧を噛ます必要があります。

出力管に5極管を使えば、スクリーングリッド電圧を高く設定することで出力管のコントロールグリッド・カソード間電圧を0Vまで振らなくても済むようになるので、その方が得策と思います。

出力管のプレート側にもセンタータップのある出力トランスを入れれば、マッキントッシュの回路のようになって、センタータップに電源を接続できるため電源が一つで済むメリットがあります。

№23 超3結FX(2001/4/29)

出力管のプレート側にもセンタータップのある出力トランスを入れれば、マッキントッシュの回路のようになって、センタータップに電源を接続できるため電源が一つで済むメリットがあります。

これ、もう少し詳しく教えて下さい

下図がかつさんのクロスシャントPPで、私は交叉型と呼んで、半導体で実験した回路がここにあります。

出力トランスをカソード側からプレート側へ移動すると下図のようになります。

出力トランスを2分割してカソード側とプレート側に入れると下図のようになります。

出力トランスのセンタータップに電源を接続すると、下図のように電源が一つで済みます。

このままではB級動作の場合、カットオフした出力管側の出力トランスのコイルが開放状態になり過渡振動を発生しますが、マッキントッシュは1つの出力トランスにカソード側とプレート側のコイルをバイファイラ巻きして結合を密にし、能動状態にある側の出力管によってコイルを常にダンプするようにしています。

5極管やビーム管の場合は下図のようにスクリーングリッドを接続します。こうするとスクリーングリッドとカソード間の電圧は常に一定にできるからです。ドライブ段のプレート負荷抵抗もスクリーングリッドの所に接続すれば、ドライブ段がカットオフまで振れなければならないような動作をせずに済みます。

この回路を実現するにはバイファイラ巻き出力トランスを自作するか、さもなければA級動作でやるしかないと思います。

出力トランスを自作については、亀さんがバイファイラ巻きは絶縁耐圧の点で二の足を踏んでいました。代わりに一層毎交互に巻くサンドイッチ巻きならアマチュアにも可能ということです。

そうした点を考えると、かつさんのフローティング電源を使った方法が、作りは大変に見えるが、実は既存部品で高い基本性能を出せる優れたやり方であるということが認識できます。

№24 超3結FX(2001/5/4)

超3結FXでは下図のように、出力電圧はドライブ管の内部抵抗rpとRbiasで分圧されて出力管のグリッド・カソード間に帰還されるので、100%帰還のカソードフォロワにはなってません。

rpに対してRbiasを大きくすることができれば100%帰還に近づけると考えられるので、EVの回路がしている下図のようにRbiasを対抗する出力管のプレートに接続することを提案します。出力管プレート電源の変動が問題になるなら対カソードで安定化すればよいでしょう。

№25 超3結FX(2001/5/6)

下側のSGはこのようにするか、3結にするしかないでしょう。

私が考えていた超3結Ver.4とマッキントッシュのフュージョン版はこんな回路です。

№26 アクティブロードNFB(2001/5/20)

図1

図1は初段電圧増幅管V1のアクティブロードである定電流回路Q1に出力管V2のプレートからNFBを掛けた回路で、出力トランスの1次側を低インピーダンスで強力にドライブできる。

Q1のバイアス電圧EBを調整することで出力管のプレート電流を調整する。

この回路では初段電圧増幅管がNFBのループ外になっているためV1の歪が減ることはない。

図2

V1をNFBのループ内に入れるためには、Q1のエミッタに接続してある帰還抵抗RNFを、図2のようにV1のカソードの方に接続し直せばよいが、そうすると電源ノイズが一緒に帰還されるため、NFBによってノイズを引き込んでしまう結果となる。

図3

図3は図1のアクティブロード側に入力信号を与えるようにした回路。

№27 DCバッファーアンプ(2001/5/24)

バッファーアンプとは高インピーダンスで入力して、低インピーダンスで出力する、ゲイン1の回路です。

入力インピーダンスを高くするため真空管を使用しました。

V1とV2、及びQ1とQ2は特性のそろったペア素子であることが望ましい。

№28 DC1段増幅器(2001/5/24)

V1はカソード接地増幅である。

V2は増幅作用をせず、無信号時のV1のプレート・カソード間電圧と等しい電圧を、V2のプレート・カソード間に発生させる。

、無信号時の出力電圧を0にする。

V1のプレート電圧の変化はそのままV2のカソード電圧の変化となる。

№29 CE分割位相反転(2001/5/27)

定電流回路によってブートストラップコンデンサーを廃した、CE分割位相反転回路。

図1

図1は一般的な位相反転回路の負荷抵抗が出力段SITのゲート・ソース間に入る接続。

図2

図2はフッターマン方式。一見、出力段SITのドレイン・ゲート負帰還回路を形成しているように見えるが、下側SITのゲートは位相反転回路トランジスタのエミッタで定インピーダンスドライブされるのでドレイン・ゲート負帰還は作用しない。

亀さんからBBSネタになればとのご好意で頂戴したマッチング・トランスをご披露します。

私だけ恵まれてしまって、亀さんのトランス欲しがってる他の皆さん、本当にすみません。

頂いたのは、かめさんのトランス工房のページにある32Ω:4-8-16Ωのマッチング・トランスです。

巻線の内容が詳しく載っていますのでご参照ください。

先ずは私の6C33C-B SEPP OTLステレオパワーアンプにつないでヒヤリングテストにかけてみました。

32Ω端子をアンプの出力に接続し、8Ω端子にスピーカを接続しました。

アンプに取ってはOTL時の4倍の負荷になり、同じ出力なら電圧振幅が2倍、電流振幅は半分の動作になり、大電流動作が苦手の真空管は負担が軽減されて出力段の歪が減少します。

山下久美子のTHE

HEARTSを中心に聴いてみましたが、マッチング・トランスを入れると一聴して、刺々しさが無くなり聴き易くなったという印象を持ちました。ヴォーカルが浮き立って明瞭になったようにも感じます。適度な緩衝材が入ったというようなイメージです。

反面OTL時よりも活気が薄れたことは事実ですが、OTL時の音はハッキリ言って聴き疲れする音で、それをアンプの発熱が大きいためという別の理由にすり替えて、長時間アンプを稼動するのを躊躇させていたのかも知れません。

マッチング・トランスを入れるとアンプが幾ら発熱して何時間稼動していても気にならない程の音になると言ったら大袈裟ですが、そんな感じです。

次は測定データ―を取って検討してみたいと思います。

簡単な測定をしてみました。

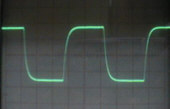

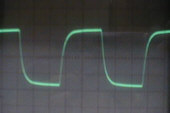

下の写真は100kHz方形波の出力波形で、上はOTL時で、下がマッチング・トランスを通した時です。

マッチング・トランスを通すと若干角が落ちます。

下図は周波数特性で、測定周波数範囲は20Hz~100kHzです。

青色のラインは0dB=1W(1kHz)、赤色のラインは0dB=10W(1kHz)の両方共マッチング・トランスありの特性です。

参考に0dB=1W(1kHz)でOTLの特性を黒色のラインで記入してあります。

歪率は1W出力時、

100Hz 0.0018%

1kHz 0.002%

10kHz 0.01%

出力インピーダンスは 0.22Ωでした。

オートトランスの電流観測

実際にどんな電流が流れているか見るために下図の方法で電流波形を観測してみました。

IpとIsを観測するために0.1Ωの電流検出抵抗を入れて0.1Ω両端の電圧をDSO(デジタルストレージオッシロ)で観ました。

一応DSOは、ch1とch2が絶縁されているタイプなので、このような接続が出来ます。

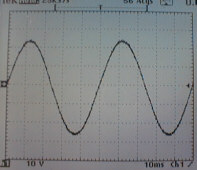

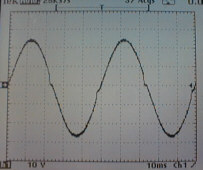

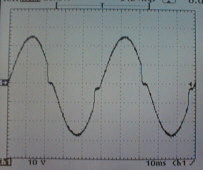

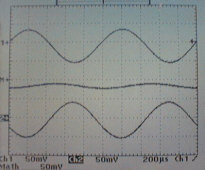

写真は負荷の8Ωに1kHZ 4W与えた時の波形です。

上がch1のIp波形、下がch2のIs波形で、中央はch1とch2を加算した波形です。振幅スケールは全部同じ(50mv/div)です。

IpとIsは位相が逆ですが振幅は等しく、僅かに位相にずれがあるように見えます。

ここまでの私の解釈を下図で説明すると、負荷を通してp側に電流が流れることでs側に電圧が生じ、s側からも負荷に電流が流れるです。

このように考えたら如何でしょうか。

1次側は出力端子までの巻線で、2次側は出力端子からCOM端子までの巻線と考えると、巻数と電流の関係が明解になります。

下図のようにIpは1次側p巻線を通り負荷に流れ、Isは2次側s巻線から発生して負荷に流れる。従って出力電流 Io=Ip+Is となる。

マッチングトランスの変わった使い方

図のようにp巻線出力とs巻線出力を分離して、それぞれに負荷を接続する使い方を試してみました。

V1に1kHz

1Vを与えた時、Vo1=0.48V、Vo2=0.49Vでした。32ΩとCOMの端子を入れ替えても同じ結果でした。

この差はトランスの伝達効率の問題ではないかと思います。

伝達効率はさて置き、このような使い方が利用できる用途は何か有るでしょうか。

ソフトン Rコアシングル出力トランス RW-20

予て注文してあったRW-20が本日到着しました。第一印象は重量が軽いこと、ケースを外すと本体サイズはケースの半分程度の厚みです。

同サイズの亀さんのマッチングトランスと並べて見ると薄くてスマートですが、その分使われている銅線の量も少ないです。

ボビンとコアの隙間が最大2mm位あることも気になります。

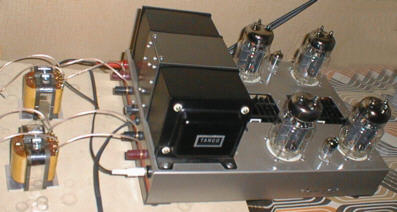

取り敢えず以前作った300BシングルアンプのタンゴXE-20Sと取り替えて見ました。

XE-20Sは5kΩ対8Ωで使用してましたが、RW-20は2次側が6Ωであるため、2次側に8Ω負荷を接続すると5kΩの1次側は6.7kΩとなり、300Bの動作ラインが変わるため、前の動作点のままでは最大出力時に出力波形の下側が先にクリップします。

そのため、プレート電流を10mA減らして70mAにしました。これによって最大出力は8.5W(8Ω/1kHz)になりました。

尚、このアンプはプレート電流の検出を、出力トランス1次側の巻線抵抗の電圧降下で行っています。

RW-20の1次側巻線抵抗は129Ωでしたのでプレート電流70mAの電圧降下は9Vとなり、XE-20Sの場合と0,2Vしか違わないので、再調整しなくても使えます。

音質的には変化が感じられませんでしたから、特性的に大きな差はないと思えます。

2001/8/12

MJ9月号24Pに交差接続型位相反転回路を使った真空管アンプが載っています。

山川正光著内外真空管アンプ回路集の63Pに交差型はクロスシャント位相反転回路ともいわれると書いてあり、この回路を使ったアンプとして24Pに1953年アメリカのスタンレー・ホワイトが発表したホワイト・パワートロン・アンプが、また84Pにチャイルズ・アンプが載っています。

〔図1〕 交差接続型位相反転回路

図1に交差接続型位相反転回路の一例を示します。

V2とV3のグリッドがそれぞれ対向するV3とV2のカソードに接続されていることがこの回路の特徴です。

V1とV4はカソード結合でV2とV3に入力電圧を伝えるだけの働きしかしていませんから、主要なコア部分はV2とV3の回路であり、V1とV4を省いて直接にV2とV3へ入力電圧を加える方式にすることが可能です。

〔図2〕 定電流電源による交差接続回路

図1のコア部分を定電流電源で吊ると図2のようにシンプルな形になります。

〔図3〕 フローティング電源による交差接続回路

出力段の回路をフローティング電源を使って考えてみましたが、図3のようにスプリット巻の出力トランスでも使わない限り回路が成り立ちません。

〔図4〕 CSPP

グリッドを対向するカソードへ接続することにこだわらなければ、CSPP(クロス・シャント・プッシュプル)と呼ばれる回路に展開できます。

〔図5〕 電流飽和しない差動アンプ

図1のV1,V4をPNPトランジスターに置き換えると図5のようにシンプルな回路になります。

この回路はV1とQ1、V2とQ2が直列接続であるため出力電流が飽和しないことが特徴です。

差動回路はリミッタ回路に利用されるように出力電流が飽和する性質のものであるため、NFBアンプでは過渡的状態などで大入力が加わった場合に歪が発生する問題を抱えてます。

しかしこの回路を差動回路と代えて採用すれば過渡歪を生じ難いNFBアンプを作ることが可能となります。

V1,V2の代わりに真空管と同じデプレッション型のJFETならば、このままの回路で置き換えることが可能ですが、バイポーラトランジスタやMOS-FETではバイアス回路を設ければなければなりません。

出力はQ1,Q2のコレクタ側からも取出せます。

〔図6〕 コンプリメンタリJFET交差接続回路

図6はオールJFETで構成し、図5の接続を上下対称にひっくり返しました。このようにもできるという例です。

無信号時のドレイン電流は下側PチャンネルJFETのIdssになります。

下側JFETにソース抵抗を入れることでドレイン電流を減らす方向に調整できます。

〔図7〕 B級プッシュプル出力回路

図7は位相反転とプッシュプル動作を一つの回路でこなす出力段です。

前段で位相反転を行い、正相と逆相の信号を左右それぞれのベースに与えるようにも出来ます。

バイアス電圧をツェナーダイオードで作るようにしてありますが、これはB級動作を想定したからで、A級動作ならCRによる自己バイアス方式でかまいません。

しかし電流飽和しないという回路の特徴を活かすためにも、B級動作とするべきでしょう。

2001/8/30

フォックスロットドライバー (by taro)

ホックスロット・ドライブはトラ技の旧号に載っていたもので

下図のような回路です.70−80年代にV−FET,SIT,

パワーMOSFETが出た時の解説記事中に出ていました.

コンプリメンタリ・ドライブと並べて,異極性の素子が無いときの

ドライブ回路として紹介されていました.

現在では,いろいろ変形されるにしろ原型は誰がやってもこうなるでしょう.

当時は,バイポーラ流にドライブトランスか,インバーテッドダーリントン

による準コンが多かったのではないでしょうか?

それに比べて,この回路は新規性があったと思います.

トラ技にはスペルも出典も出ていませんでした.

事情があってトラ技のアナログ関係の記事調査中に見つけました.

経緯が明確になれば紹介しやすいんですが.

2001/9/6

SITのドレイン電圧の変化に対し、ドレイン電流を一定に保つ方法。

SITはドレイン内部抵抗が低い3極管特性の素子であるため、固定バイアスではドレイン電圧の変化に連れてドレイン電流が変化します。

内部抵抗が低いと少しのドレイン電圧の変化でもアイドリング電流が大幅に変化して、アイドリング電流が減少した場合には歪が増え、逆に増加した場合にはドレイン損失が増大して壊れる危険があります。

アイドリング電流を一定化するには以下の対処法がありますが、問題もあります。

1)自己(セルフ)バイアス方式は直流分を電流帰還で定電流化する仕組みであるためDCアンプには使えません。

2)定電流源を電源とする差動プッシュプル方式は電力効率の悪いA級動作でしか使えません。

3)カスコード接続でドレイン電圧を固定してしまうと、SITの内部抵抗の低さを活かせません。

真空管回路で電源電圧変動に対して3極管のプレート電流を安定させるために使われた手法の焼き直しですが、ドレイン電圧の変化をバイアス電圧に加えることで、ドレイン電流を一定に保つ方法があります。

SITのドレイン・ソース間電圧の変化分ΔVDSに対するドレイン電流の変化分ΔIDはドレイン内部抵抗rDに反比例する。

ΔID=ΔVDS/rD

また一方SITのゲート・ソース間電圧の変化分ΔVGSに対するドレイン電流の変化分ΔIDは相互コンダクタンスgmに比例する。

ΔID=ΔVGS gm

ドレイン・ソース間電圧の変化によるドレイン電流の変化をゲート・ソース間電圧の変化でキャンセルするためには、

ΔVDS/rD-ΔVGS gm=0

とする。

ΔVGSを求めると、

ΔVGS=-ΔVDS/(gm rD)

gm rD=μだから

ΔVGS=-ΔVDS/μとなる。

つまり、ドレイン電圧の変化分の1/μを逆相でバイアス電圧に加えると、アイドリング電流を一定に保つことができます。

2001/9/6

電源ノイズをキャンセルする3極管出力回路

3極管はプレート内部抵抗が低いために、固定バイアスでは電源電圧の変化に連れてプレート電流が変化してしまい、電源のリップルノイズが出力に混入したり、プレート電流が減少した場合には歪が増えたり、逆に増加した場合はプレート損失が過大になるといった不具合があります。

プレート電流を一定化するには以下の対処法がありますが、問題もあります。

1)自己(セルフ)バイアス方式は直流分を電流帰還で定電流化する仕組みであるためDCアンプには使えません。

2)定電流源を電源とする差動プッシュプル方式は電力効率の悪いA級動作でしか使えません。

3)カスコード接続でプレート電圧を固定してしまうと、3極管の内部抵抗の低さを活かせません。

電源電圧の変化をバイアス電圧に加えることで、プレート電流を一定に保つ方法があり、その回路の一例を下図に示します。

この回路はPNPトランジスタTRによって3極管VTのカソードに電源電圧VBの1/μを加えています。

その結果、VTのプレート電圧はVBの1/μの電圧のμ倍の電圧、つまりVBと等しくなるため、プレート電流に変化を生じません。

VCは任意のプレート電流に設定するためのバイアス電圧で、設定するプレート電流に応じて極性を変える必要があります。

この方法の一般的な応用を考えて、下図のようなOPアンプを使った回路に展開して見ました。

左は反転増幅器で右が非反転増幅器として動作しますが、差動増幅器の変形です。

負荷側に加わるノイズ電圧ENと同じ電圧がOPアンプの出力に発生するため、負荷の両端に電圧差が生まれません。

RBは信号源のインピーダンスを含めた値です。

負荷がスピーカで、スピーカコードが拾うノイズに影響されないようにするには、RA,RCの接続点をボイスコイルの所にする必要があります。

超3極管接続への応用を考えたのが下図です。

VT1,TR3,VT3で超3極管接続Ver.2を形成しています。

VT2のカソードにはVBの1/μが発生し、それをTR3がVT1のカソードに加えているので、VT3のプレート電圧とVBが等しくなります。

TR1,TR2によって信号分を加え、CC3でVT3の動作点の電流を調整します。

この回路で第2グリッド電圧VG2は定電圧電源を想定していますが、VB同様の非安定電源の場合は第2グリッドのμを考慮した対策が要ります。

2001/9/28

2001/9/30

トラッキングバイアスで電源ノイズをキャンセルする

超3極管接続Ver.1 6LU8シングルパワーアンプの実験

トラッキングバイアス

内部抵抗の低い3極管は電源電圧の変動によってプレート電流が変化するため、電源電圧に整流後のリップル電圧が乗っていると、プレート電流がリップル電圧に比例して変化し、プレート電流の変化は出力トランスを通して出力されるためハムノイズが発生します。

内部抵抗が3極管とは桁違いに低い超3極管接続ではその影響がより顕著であり、これまで電源のリップルフィルタを強化することと、直流的な電流帰還作用を使った自己バイアス方式などで対処してきました。

新しいアイデアとして今回採用したトラッキングバイアスとは、電源の電圧変動に追随してバイアス電圧をコントロールすることで、電圧変動によるプレート電流の変化をなくそうという考えのものです。

動作的には電源電圧の変動分を適量だけ信号電圧に加えて、プレート電圧を電源電圧の変動と等しく変化させることで、出力トランスの1次巻線に電位差が発生しないようにします。このため信号電圧に加える電源電圧の変動分の量は、電源電圧の変動分÷バイアス部分からプレートまでの電圧ゲインという計算で求めることができます。

アンプ回路

電源回路

今回使用した6LU8は3極5極の複合管で、3極部のμは6BM8と同じ60で、5極部のプレート損失は6BM8の2倍の14Wもある12ピンのコンパクトロン管です。

そのため主な定数は6BM8の時のままで、5極部のプレート電流だけを6BM8の時の2倍の70mAにして動作させました。

バイアス部分からプレートまでの電圧ゲインは概算で、6LU8

3極部グリッド・カソード間抵抗5.6kΩ÷初段2SJ103のソース抵抗1kΩ×6LU8

3極部μ60で計算でき、およそ300となります。

電源電圧の変動分を、2SA872Aのエミッタ抵抗470kΩ÷VR1でおよそ1/300にして、初段2SJ103にバイアス電圧を与える2SC1775Aのベースに加えています。VR1の調整は出力のノイズが最小になるポイントにセットします。

2SK30ATMはバイアス電圧を調整するための定電流回路で、VR2で6LU8

5極部のプレート電流を70mAに設定します。

直流電源は3つ必要です。V1-V2間は6LU8

5極部のプレート電源で、電圧は約200Vです。コンデンサーインプット整流だけではリップル電圧に高い周波数成分が含まれているので、CR1段のフィルタでリップル波形を滑らかにしました。リップル電圧は0.2Vp-p程度です。このリップルフィルタの300Ωの電圧降下でプレート電流を測定します。

V2-GND間の電源は、6LU8

のグリッドバイアスとグリッド入力信号電圧の大きさで必要な電圧が決まり、50V以上あれば大丈夫と思われます。電流は1mA程度しか必要なく、定電流性の回路が対象なためリップル分があっても問題ありません。

GND- -V間は初段2SJ103のドレインと2SK30ATMの定電流回路の電源で電圧は6V~15Vあればよく、電流は1mA程度、定電流性の回路であるためリップル分があっても問題ありません。

調整はVR1とVR2を最大の状態にしておき、先にVR2でプレート電流を70mAより少なめに設定しておきます。VR1をまわすとプレート電流が増加するので、70mAになったらまたVR2でプレート電流を70mAより少なめに設定しなおしてからVR1を調整します。VR1を調整して出力のノイズを最小にします。

出力に発生するノイズは入力ショート、出力8Ω負荷で60μVにできました。CR1段のフィルタのコンデンサを外すとリップル電圧は4.5Vp-p程度となり、出力のノイズは150μVになります。そのノイズ波形を観るとリップルの高い周波数成分がキャンセルされていないため、リップル電圧を小さくすることよりも高い周波数成分を減らすことの方が効果的と考えます。

その他の特性は

最大出力3.5W

歪率 100Hz 1W 2.4%、1kHz 1W 2.4%、10kHz 1W 2.6%

出力インピーダンス 0.8Ω

2001/10/8

超3極管接続Ver.1 6LU8シングルパワーアンプwith電源ノイズキャンセラーの実験 2

部品数を減らす目的でノイズキャンセル信号の注入場所を初段トランジスタのコレクタ側にしてみましたが、逆に部品が増えてしまいました。

それでもトランジスタは2石だけになったし、マイナス電源が不要になりました。

下図のように2つの回路を考えましたが、実験したのは上の回路だけです。

実験回路

未確認回路

実験回路の調整方法は100kΩVRと10kΩVRは最大にしておき、先に10kΩVRでプレート電流を70mAに設定して、次に100kΩVRを調整して出力のノイズを最小にします。100kΩVRを回すとプレート電流が減少するので、10kΩVRでプレート電流を70mAに設定し直して再度100kΩVRを調整するという作業を繰り返します。

半導体の温度変化によるものと思いますが、電源投入から少しずつプレート電流が減少して行き、安定するまで数分かかります。

初段がトランジスタだけになったので、歪率が前より減りました。

100Hz 1W 0.42%、1kHz 1W 0.26%、10kHz 1W 0.50%

2001/10/16

超3極管接続Ver.1 EL34PPパワーアンプの実験

超3極管接続Ver.1シングルの回路を2つプッシュプル接続しただけの回路です。

出力管はAB級動作です。

電源ノイズキャンセル回路とプッシュプル接続のダブル効果で残留ノイズ30μVをマークしました。

出力トランスは2次側4Ω端子に8Ωを負荷することで、1次側インピーダンスを5kΩにしています。

EL34は Svetlana

、12BH7はSLNグレードのラム管を試用してみました。

流石SLNグレードの賜物で残留ノイズ30μVと言いたいですが、どっこい以前ハムノイズ大で跳ねてあった12AU7を使っても40μVになりましたから、誉めるべきは回路の方です。

残留ノイズ30μVをキープするにはVR1で2本の出力管のプレート電流が等しくなるように調整していなければならないので、自動的にバランスを制御する回路を考えて見ようと思います。

最大出力 18W

歪率 1kHz 1W 0.025%

出力インピーダンス 0.2Ω

2001/10/17

超3結Ver.16BM8s2のバイアス回路

2001/10/28

クロスシャントPK分割

2001/10/30

クロスシャントPK分割

2001/11/1

超3極管接続Ver.1 EL34PPパワーアンプの決定回路

2001/11/2

野呂さんのアンプ回路

デカップリング回路と発振防止抵抗などは割愛しました。

ついでにブートストラップすると下図のようになります。

Rは出力と並列になるので小さすぎるとパワーロスになりますから1kΩ~10kΩといったところ、CはRとの時定数で適当に決めてください。

2001/11/10

回路変更

初段差動2SK389のソース間抵抗を固定抵抗にしたことが原因で電源リップルノイズが出力に発生すると解ったため、再びトリマーに戻しました。

でもどうしてDCサーボで電流をバランスさせただけではダメなのか分かりません。

DCサーボの積分コンデンサーが100μFでは低域ゲインが低下するため増量しました。

高域特性が悪化するため初段差動出力の位相補正は取り除きました。

オープンループゲインを下げるため、帰還管カソード・グリッド間の抵抗を5.6kΩに減らしました。

前回の回路では電源変動キャンセルが不十分であったため、その前のようにアイドリング電流設定用のトリマーを追加しました。

調整方法は初めに、2SK389のNFB側ゲートを接地し、VR1,VR2は中央に、VR3は最大、VR4は-40Vの方に回しておきます。

真空管のヒーターを別電源で点火しておいて、他の電源のAC100V側は共通にしてスライダックで徐々に電圧を上げ、電源電圧を上げてもプレート電流が増加しない所までVR3を回します。この時VR3を回すとプレート電流は減少するのでVR4を回してプレート電流を適正値にします。

出力のノイズ波形をVR1で最小にします。2SK389のNFB側ゲートの接地をはずして、VR1で両EL34カソード間の電圧差を0に設定します。

いつものパターンで、既に主要パーツは集まったというのに定数の決定に悩んでいます。

(1)出力トランス2次側からの帰還を掛けない場合

ゲインを20倍程度にするため初段差動2SK389のソース間抵抗を200Ωとした時、

出力インピーダンスは1Ω程度

周波数特性は150kHzで-2dB

歪率は1W出力時、100Hz、10kHz、10kHzで0.05%位

このままでも充分なデータ-が得られました。

(2)出力トランス2次側からの帰還を掛けた場合

初段差動2SK389のソース間抵抗を100Ωとし、オープンループゲインを30倍程度し、回路図の通り100Ω/2kΩのNFBを掛けた時、

電圧ゲインは15倍程度、従って6dBの帰還量となっています。

出力インピーダンスは0.2Ω程度

周波数特性は150で-0.5dB

歪率は1W出力時、100Hz、10kHz、10kHzで0.03%位

10kHz方形波の容量負荷安定性は0.1μFのみ負荷すると、辛うじて発振には至りませんが激しいリンギングを発生します。

出力トランスが入ると僅か6dBのNFBもままならないことを痛切に感じます。

アンプ内で高域ゲインを落とせば安定しますが、高域特性は無帰還時よりも悪くなり、そういうアンプに対して私は体質的に拒絶反応してしまいます。

この拒絶反応は一種の精神疾患で、放っておくと症状が悪化してあらゆるものを受け付けなくなったりして、簡単なカウンセリングを受ければ直る程度のことかも知れません。昔はどんなものにも愉しめたのに、どんどん愉しい物が減っていくような気がします。愉しさを取り戻すために無茶苦茶なアンプを作る勇気が今必要なんだとふと考えました。

でもそんな勇気は出て来ないから、愉しい物を減らす愉しみという、屈折した欲望のままに生きる今の自分を放っておくよりほかしゃあないってことで、その先、全てを無にして無想転生の奥義でも手に入れようかと思ってます。

2001/12/1

AOCの先に見えるもの

MJ12月号DCアンプシリーズNo.165はAOCの働きでDCアンプではなくなっているというのに、フロントパネルには偽りの-DC-のプリントが堂々と、でもこれを額面通のDCアンプとすることができます。

AOCの差動アンプの接地されている側のゲートに、Inputからの信号電圧を分圧器で適当な大きさにして入れてやればよいのです。

こうするとAOC側が信号増幅するので、初段差動アンプのInput側の信号電圧とNFB側の帰還電圧が等しくなるように分圧器を設定しておけば、初段差動アンプには入力電圧が発生せず、帰還電圧に歪が含まれていれば、歪分だけが初段差動アンプの入力電圧となるため、初段差動アンプは大振幅な動作はしなくてよくなるため歪が低減します。

この方式はLuxmanのODNF回路(Only Distortion Negative Feedback)と一緒です。

真空管を使った初段差動アンプの方が副アンプですから、真空管を主アンプにしたければ、FETを使った差動アンプの方にNFBをかけて、真空管を使った差動アンプの方をAOCに、んなバカな、ドリフトの大きい真空管でAOCはできませんが、FETを使った差動アンプのドリフトは少ないのでAOCは不要です。

2001/12/8

ちょっと改良の回路の実験

まだ私も実際の回路での動作を確認してないので、回路を組んで実験して見ました。

この程度の回路は御茶の子さいさいで正味1時間もかからずに作れましたが、案の定オッシロには発振波形の帯が出現、終段のトランジスタを取り替えたりベースに抵抗を挿入したり、いろんな所へCやRやLを入れて見ましたが、方形波の通りが悪くなったり、リンギングが出たりと、どうも果々しくなく、ちょっとお手上げ状態です。後は回路シン様にさじを預けます。

もとの回路の定電流源の箇所は15kΩの抵抗にして、電源電圧でアイドリング電流を調整するようにしてあります。

15kΩの側と680Ωの側は1:1のカレントミラーになっているので、無信号時は15kΩと680Ωの電流が同じであるため、15kΩの電流でバイアス電圧の調整ができるわけです。電源電圧17Vで終段のアイドリング電流は約0.1Aとなりました。

発振以外はちゃんと動作しますから、我と思う方は挑戦してみてください。

2001/12/9

前の実験でバーポーラトランジスタの4段ダーリントンはどうにも発振が治まらないので、アイデアのエッセンスだけ頂いて、私風にアレンジしてみました。

出力段をパワーMOS-FETにして、誤差増幅はJ-FETのゼロバイアス動作を使いました。

無信号時のバイアス電圧はJ-FET(2SK163/2SJ44)のIdss(約4mA)と1kΩVRの抵抗値で決まります。

2つのVRを交互に調節して、出力段MOS-FETのアイドリング電流と、OUTのオフセット電圧を調整します。

パワーMOS-FET(2SK1529/2SJ200)のVgsは約2VなのでVRの抵抗値は350Ω位となっています。

INを接地すると微小発振するため100Ωを直列に入れてあります。

どうにかこの状態で発振することなく安定に動作します。

出力インピーダンスは0.2Ωで、J-FETのソースとOUTの接続をはずした状態の出力インピーダンスが0.7Ωでしたから、効果のあることが確認できました。

2001/12/10

最上下のトランジスタのベース・エミッタと並列の抵抗(R)の電圧(Vbe)を一定にするため、その一つ内側のトランジスタが働いていて、Rの電流を定電流化しているわけですね。

正入力側トランジスタのコレクタ電流をIc1、負入力側トランジスタのコレクタ電流をIc2、出力側トランジスタのコレクタ電流Ic3とすると、Vbe/R=Ic2+Ic3という関係になっている。最上下のトランジスタのエミッタ内部抵抗をreとすると、左図の方法ではVbeはre・Ic1だけ変化するので、むしろ片

肺にした右図の方が低歪であるというわけですね。

差動出力を活かせないのはもったいないので、下図のようにカレントミラーで差動出力をプッシュプル合成する方法を考えてみましたが、いかがでしょうか。

また下図のように電流帰還形アンプへの応用を考えてみました。

2001/12/13

ひとつめの回路はODNFと同じ動作原理ですから、Q2でのゲインを上げなければ歪が減りませんから、Q2でのゲインを殺したらこの回路の存在価値がありません。

今これをZDRに変更することを考え中です。

ODNFとZDRの違いを端的に説明すると、ODNFは基本的にNFBであり、NFBはアンプの入出力の誤差分を入力に加えることで、入出力の誤差が減るわけですが、そうすると入出力の誤差分減ってしまうために、誤差をより小さくするには、より小さな誤差を検出できるようにアンプのゲインを上げなければなりません。NFBでは誤差分を増幅するアンプのゲインが高いほど低歪となるわけです。

NFBアンプは誤差分をキャンセルするための信号の加算ポイントが、誤差を検出している範囲の中にあります。

ZDRはフィードフォワードに類似のからくりで、NFBアンプと違って誤差を検出している範囲の外に誤差分をキャンセルするための信号の加算ポイントがあります。そのため検出される誤差分が減ることはありませんから、誤差分を増幅するアンプのゲインはその系に適した値に設定すすることで、歪を完全に打ち消すことが可能となります。

ODNFはNFBの仲間。

フィードフォワードは出力側で歪キャンセル分を加算。

ZDRは入力側で歪キャンセル分を加算。

D-NFBはZDRと同じ。

2001/12/15

ZDRにするためには、誤差検出の場所をINからダーリントントランジスタのベースに変更すればよいだけですが、回路シンさんの回路はバイアス回路と誤差検出回路が渾然一体となっていて簡単には変更できないので、私のへなちょこ実験回路を 下図のように改造しました。

VR3で誤差検出回路のゲインを調整できます。このゲインを調整抵抗分には2SK163/2SJ44のソース内部抵抗が含まれますから、本来は2SK163と2SJ44のソースそれぞれにVRを入れて調整しなければなりませんが、回路を簡素化するためにVR共通にして、2SK163/2SJ44のドレイン間に大容量コンデンサーを接続して低インピーダンスで結合しました。このような手抜き工事の代償として、電源投入時にコンデンサーが充電されるまで過大なバイアス電圧が発生してしまうため、その時間が過ぎるまで2SK1529/2SJ200のゲート間に入れたSWをONするという余計な手間が掛かるようになりました。回路図上はSWになっていますが実態はクリップ付コードです。

VR3の調整で出力インピーダンスはゼロにもマイナスにもできます。

歪率最小ポイントにおける出力インピーダンスは0.1Ω位、この時の歪率は1kHz、8Ω負荷、1W出力で0.5%でした。

この歪は誤差検出回路とバイアス電圧制御回路によるものと思われますから、その部分の歪を減らすことが課題です。

2002/1/9

2台のアンプの違いを検出する方法。

2台のアンプの出力を引き算して発生した差分が違いである。差分を完全に0にすれば完全に同じアンプになるだろう。

2002/1/20

出力を直接見ない制御方法

これは既知のインピーダンスZkが負荷と直列にある場合、出力電圧Voを直接見ずに、Zkの手前の電圧Vsと電流Isから、

Vo=Vs-IsZk と算出できるので、これをフィードバック信号などに使おうというアイデアです。

下図のACUは演算回路にVsと、電流検出抵抗Raによる電圧Vaを与えることで、Vs-Zk(Va-Vs)/Ra=Voを得て、それをβを介してアンプAに負帰還する回路で す。

応用として、D級アンプの出力ローパスフィルターの流入電流と電圧パルス幅からVoを推定してNFBを掛けることができる。

2002/1/21

出力インピーダンスをゼロにする回路

電圧ゲインAのアンプに入力電圧Vinが与えられると、出力にはAVinの電圧が発生し、出力電流Ioが出力インピーダンスZoを通って負荷に流れ出力電圧Voが発生 し、Vo=AVin-IoZoとなります。

そこでもしVinにIoZo/Aという電圧を加算することができれば、

Vo=A(Vin+IoZo/A)-IoZo=AVinとなり、Zoの影響が無くなり出力インピーダンスがゼロになります。

下図の回路でZaをZo/Aに設定しておけば、ZaにはIoZo/Aという電圧が発生するので、これをVinに加算することで出力インピーダンスをゼロにできます。

2002/1/26

最近購入したもの

スイッチング電源 イーター電機 BJB06SA

これは真空管のヒーター電源に使うつもりです。

5Vとか12Vはありますが、6Vは少ないですね。

ラジオ技術の広告にあった三協電子部品にメールで注文したら在庫ないため納期1.5ヶ月とのこと、急ぐ要はなかったので代金振り込んだら1週間足らずで届きました。

しかも航空便で、大阪と松本は定期便が飛んでいるので、赤字で早く路線廃止になった方が私的には静かになってうれしいですけど、こんな利用で少しでも延命に手を貸したかと思うと悔しいです。

届いた品物には説明書一つ付いてません。でも大丈夫、イーター電機のHPにデータシートがあるのでそれをプリントアウト。

出力6V,最大4.8Aで電圧は±5%可変できます。

ボードタイプなので低価格ですが端子がオスのコネクタになっています。

適合するメスコネクタを探すのが面倒だし、コネクタの接触抵抗が経年変化で増加することがあるので、端子に配線を直接半田付することにします。

通電テストしてみると、1Ω負荷でリップル電圧は90kHzで20mVp-p程度でした。入力60V位から安定した出力が得られます。

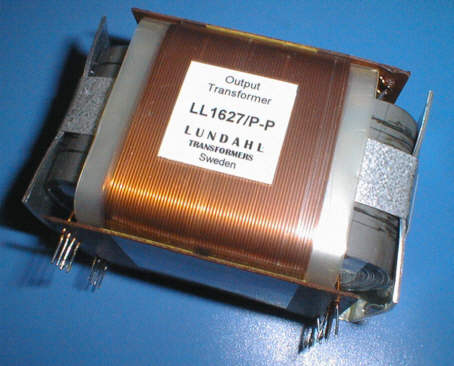

出力トランス Lundahl LL1627 P-P

ランダールと発音するのでしょうか、アンドレアさんのHP(表口が重いので勝手口から失礼します)で見かけていてアムトランスで取り扱っていたのでつい衝動買いしました。

SITアンプに使えないかと考えています。

これも説明書一つ付いてません。でも大丈夫、ランダールのHPにデータシートがあるのでそれをプリントアウト。

今の時代、インターネットは必需品になってしまいました。それに紙の取説は汚したり無くしたら使えませんけど、その点、電子データーはよいですね。

25ミクロンのギャップの入ったカットコアで、Rコアトランスと同じ内磁型の構造です。

造りからして素(す)のトランスというイメージで、私が手巻きで最初に作るならきっとこんなトランスにするだろう程に私に近いセンスを感じます。

透明の絶縁材で巻線が見えるのが良いです。巻線の端をファイバー紙に突き通しただけのシンプルさも好きです。

カットコアを締めるバンドの端とか、3方を包んでいる鉄板のエッジで手を怪我しないかと思いましたが、その辺は気を使っているようで触ると全然そんなことはなく、これは無頓着に見せながら実はちゃんとやっていることを知らしめる演出かもしれません。

層間紙の隙間から巻線構造を観察すると、コア側から2次1層、1次2層、2次2層、1次2層、2次1層と単純です。

1次側は4つの同じ巻数の巻線から成り、それを直列に接続して使用することをメーカーは推奨しています。

2次側は8つの同じ巻数の巻線から成り、それをバランスよく直並列に接続して所望のインピーダンスが選択でき,オプションで所定の接続のプリント基板が用意されてますが、簡単な配線なのでその必要はありません。

メーカーの推奨している接続パターンは以下の6通り

A:全並列

B:2直列4並列

C:3直列2並列

D:4直列2並列

E:6直列

F:全直列

CとEは2つの巻線が余りますが、遊ばせないで隣の巻線と並列接続します。

他に5直列とか7直列もできますが、巻線の直流抵抗はできるだけ低い方が良いと考えると、AかBで、4Ωから8Ωの負荷ならBの接続がベストです。

1次側も全直列以外に、2直列2並列、全並列、お遊びの3直列と、4通りのパターンが楽しめますから、SEPPのマッチングトランスに利用できそうです。

2次側を2直列4並列、1次側を全直列にして、周波数特性を簡単に測定してみました(発信器出力5.4Vrms.,50Ω)。

6Hzから75kHzが-1dB以内、高域-3dBポイントは180kHz、240kHzから280kHzにかけて-4.3dBで一定になり、330kHz以上から素直に減衰するので、300kHz辺りに高域のピークがありそうです。

2002/3/14

詳細な回路図は以下のようになりますが、何分にも未確認(実験してない)ので動作の程は保証いたしかねます。

TL431のデーターシートを見たら最小動作電流は1mAとか、なのでシリーズ抵抗を100kΩから47kΩに変更しました。

調整方法は始めに、VR1は真ん中、VR2は抵抗が最小となる位置に回しておきます。

電源を入れ、VR2で 6LU8 5極部のプレート電流を70mAにして、VR1を少し左右どちらかにまわして、VR2で 6LU8

5極部のプレート電流を70mA設定しなおして、その時ノイズが減少したなら更にその方向にVR1を回して、ノイズの最小ポイントに設定します。

6LU8 5極部のプレート電流が減れば当然ノイズは減少するので、プレート電流が70mAの時のノイズを測定することがポイントです。

調整は耳でノイズを聞きながらやるつもりでしょうね。

できればミリボルトメーターでノイズ電圧を測定し、オシロスコープでノイズ波形を見ながら行うの方が確実です。

2002/4/2

寸法比較のためTO3のトランジスタを中央に置いて撮影。

トーキンSIT 2SK183 4個購入 @\21,500- 購入先クルミ電子有限会社

2SK183の規格(98年CQ出版規格表より)

VGDO>800V(IG=100μA)

VGSO>70V(IG=100μA)

ID=60A

PD=1000W

Cis=8000pF

個々の検査成績データの写しが付いてます。

ご好意でμ=15のものを4個そろえて頂きました.。(感謝)

取りあえず物をゲットしただけで、何を作ろうかはこれからです。

2002/4/10

文面から33kは2SC2752のベースに入ると推定して以下のような回路でしょうか。

ベース電圧が410Vなら、エミッタ電圧はそれより0.6V位低い電圧ですから大まかに410Vとして、負荷抵抗の電流が310mAならば、負荷抵抗は1.3k位でないとオームの法則に合いませんが、もし負荷抵抗の電力容量が小さいなら、過熱したことで実際の抵抗値が変化したと考えられます。

トランジスタの耐圧はコレクタとエミッタ(またはベース)の間の電圧なのでそれが500Vを超えなければよいのです。エミッタ側に大容量のコンデンサーが在ったりすると危ないですが、そうでなければ大丈夫です。心配なら500V以下のツェナーダイオードをコレクタ・エミッタに並列に接続します。

それよりも310mAという電流が気になります。

2SC2752のhfeは最大80なのでコレクタエミッタ間には最低でも130V程度の電圧が発生します。

するとコレクタ損失は40Wにもなって、最大コレクタ損失10Wの2SC2752はイチコロですよ。

2002/4/10

今日発売のMJに、ヒノ・オーディオのSITアンプ試聴会(コンテストじゃなかったの)の模様が紹介されてますが、応募者は木村さん含めて2名だけとは寂しい限りでしたね。

私のSITアンプはご覧のように仰向けに横たわって内臓摘出手術中です。

私もついに焼きが回ったみたいで、電解コンデンサーを逆極性に取り付ける詰まらんミスのため、電解コンデンサーが白い煙を上げて昇天してしまいました。他にダメージが無ければよいのですが、この先が心配です。

2002/7/2

FUJIKIさんへ

タンゴS-2063を使用する電源回路

2002/7/11

トラ技8月号に黒田さんがトランスリニア原理を使って解析している「クロス結合フィードフォワードAB級出力段」は非常に興味深いです。

MJ8月号では自作アンプコンテストの規定が補足説明されています。

出力によるクラス分けですから、極端な場合、大出力クラスのアンプの出力をリミッタで制限して小出力クラスに応募することも可能と思います。

物量に物を言わせた余裕綽々のアンプと、やっとこさっとこで規定出力に達したアンプとの対決があれば見ものです。

下の回路はコンテストの条件とその趣旨に合わせて、受け狙いで組んで見た出力6Wのアンプです。

ここに公表したために未発表という条件に触れて失格ですけど。

RAJ1は電流正帰還量を調整してDF=∞にするためのもの。

RAJ2は電源リップル電圧を初段管のG2に与えて、出力管のプレート電圧に発生する電源リップル電圧のキャンセル電圧を調整するためのもの。

RAJ3はヒーターハムを最小に調整するためのもの。

6267/EF86のシールドを必ずアースすること。

6267/EF86はノイズの少ない選別品(ゴールドエアロ・プレミアムシリーズ)を使用したのでノイズを0.5mV以下に出来たが、一般品ではDC点火の方が確実。